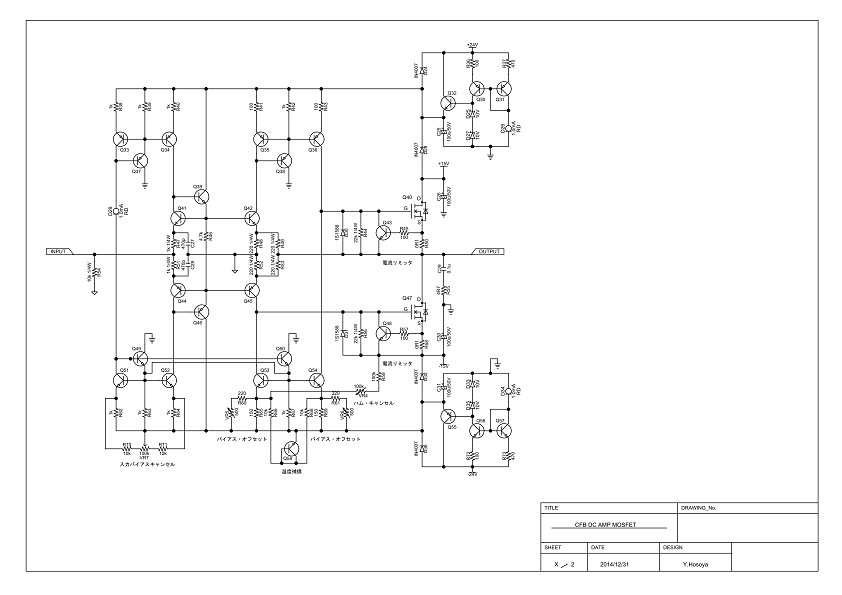

オーディオ用パワーアンプの自作

2:MOSFET DCAMP の設計

2-1:最大出力と熱設計

物理的に小さいアンプを作りたいので現実的な落としどころを探ります。 こちらで定義したように8Ω負荷で10Wの連続出力が可能なように熱設計を行います。

まず第一に大出力が不要なことから,電源電圧を低く抑えることによってアンプの発熱を抑えます。 12.5Vに対して若干余裕を見込んで±15Vを目標とします。

パワーアンプの消費電力を計算してみますと,出力電圧がDCの場合は出力電圧が電源電圧の1/2(50%)の時に消費電力が最大となります。 正弦波の場合は出力電圧が電源電圧の2/π(64%)の時にパワーアンプの消費電力が最大となります。 そして正弦波よりもDC出力の方が厳しい条件となります。

したがって,電源電圧を±15Vとすると,出力電圧が7.5Vの時にアンプの消費電力が最大となります。 8ohm負荷ではスピーカー出力電力が7.5^2/8 = 7.03Wの時にアンプの消費電力も7.03Wとなり最大値をとります。

参考までに6ohm負荷では9.38Wとなり,4ohmでは14.06Wとなります。

欲張って4ohm負荷でもある程度動作を保証しておきたいと思います。 発熱が多くなりすぎるので,ピーク電圧-12dBの法則(出力電圧1/4)を適用してパワーとしては1/8の2.5Wを目標にします。

電源電圧15V,出力2.5W = 3.16VRMS * 0.79ARMS @ 4ohmとして,アンプの消費電力は(15-3.16)*0.79 = 9.36Wとなります。

以上の数字を整理すると,6ohm負荷だとDC出力時の最大消費電力が9.38W,4ohm負荷だと音楽信号出力時の最大消費電力が9.36Wとなりますので, アンプ発熱を10W弱と考えるのが妥当と判断しました。

| 項目 | 数値 | 条件 |

| パワー段消費電力 | 6.77W | 出力電力(DC)10W,8Ω |

| パワー段消費電力 | 7.03W | 出力電力(DC)7.03W,8Ω |

| パワー段消費電力 | 9.03W | 出力電力(DC)13.3W,6Ω |

| パワー段消費電力 | 9.36W | 出力電力(DC)2.5W,4Ω |

| パワー段消費電力 | 9.36W | 出力電力(音楽信号)10W,4Ω |

| FPBW | DC〜100kHz | (フルパワーバンド幅) |

もしアンプに定格を表示するとしたら「定格負荷:4Ω〜8Ω」「最大連続出力:10W(Music Power)」となるのかなと思ふ。

全体の電力を計算していきます。 出力電力以外の発熱源としてはアイドリング電流による発熱,電圧増幅段の電力が考えられます。

アイドリング電流を200mAとすると±15Vなので6Wとなります。電圧増幅段に2W必要とするとします。 結果として片チャンあたり9.36+6+2 = 17.36W,ステレオで2倍になり34.7Wの消費電力となります。

タカチのHYシリーズの一番小さいサイズの熱抵抗が1.73℃/Wです。 ケースの温度上昇を30℃におさえると考えると都合よくぴったり収まります。 トランスの発熱もありますので,熱くなるようであればアイドリング電流を100mA程度まで絞って対応します。

なお,FPBW(フルパワーバンド幅)はDC〜100kHzの予定です。 この帯域内ならば周波数に依存せず強力に負荷を駆動できる予定です。

周波数340kHz以上では出力段のスナバーがアンプの負荷になります。 スナバーの抵抗は4.7ohmなので340kHz以上は出力パワーを制限しないとスナバ抵抗の発熱と出力段の発熱が同時に発生しアンプが非常に熱くなります。

2-2:回路トポロジー

DC結合のパワーアンプ(DCアンプ)と言えば初段がNch Dual J-FETによる差動アンプというのが定番と思います。 2段目がPNPバイポーラトランジスタによる差動,そして逆相を側をカレントミラーで折り返してコンプリメンタリーパワートランジスタをダーリントンでSEPP駆動するというのが一般的な構成です。 高校生の時に作りました。シンプルでもそこそこの性能が出ると思います。

この形式はJBLのシンメトリカルTサーキットを祖としています。 FET入力とすれば簡単にDCアンプ化できる為,金田氏のDCアンプシリーズを筆頭として長い間スタンダードな回路形式でした。

バリエーションは様々に考えられます。しかいいずれの場合でもまずネックになるのが入力のDual-FETです。 まず,入手性が悪く,入手できても値段が高いです。入力容量が大きく,カスコードしてやらないと高域での歪が悪化します。 DC安定度は全てこの初段にかかっているのでペア選別するならばそれなりに気合が必要になります。 しかも苦労してペア選別した割にオフセットや温度ドリフトが押さえきれません。

バイポーラの差動入力も考えましたが,DCアンプとするためには入力バイアス電流のキャンセル回路が必要になってしまい無駄に複雑化してしまいます。

そして致命的だったのが電圧帰還アンプ(VFB)を安定的に動作させる難しさでした。非反転アンプは本質的に不安定なのか・・・安定性を求めれば帯域が取れません。

やはり高速化を求めるのならば電流帰還アンプ(CFB)に分があるようです。

2-2-1:MOSFETを使用した電流帰還アンプ

高速動作に有利な電流帰還アンプですが,欠点もあります。

B級のトランジスタアンプでは出力段にバイポーラ・トランジスタを使いますが, バイポーラ・トランジスタはべき乗特性でカットオフが急峻なためクロスオーバー歪が必ず発生します。

アイドリング電流を大量に流してA級とすれば軽減できます。しかし,発熱が大きくなります。 トランスリニア回路のようにカットオフしない回路を工夫すれば軽減できますが,部品点数が多く,トランジスタのマッチングも必要です。

結局シンプルな回路で歪み率を抑えるためには負帰還に頼る必要があります。

ところが電流帰還アンプは裸のゲインが低いので歪みを負帰還で押さえ込むことができません。

そこで出力段にMOSFETを使ってみたところ,すべてが解決しました。 よく言われる通りMOSFETは2乗特性ですのでクロスオーバーひずみが出にくいのです。

電流帰還とMOSFETを組み合わせることで低歪率で(しかも高次の歪みがでにくい)高速,高安定な回路ができました。

しかし,いくら速いと言っても,Pch MOSFETが遅いのです。 Nch MOSFETに比べるとPch MOSFETは半分のスピードしかありません。遅い方に合わせて足を引っ張られてしまいます。 オーディオ用のコンプリメンタリMOSFETでも動特性まで一致するとは限りません。

しかも,出力段の速度がアンバランスの回路に立ち上がりの早い信号を入れるとバランスが崩れて貫通電流が流れてしまう現象が見られました。

コンプリメンタリFETを使用せずに,同極性のNch MOSFETを二つ使ってなんとかSEPPにできないか方策を探りました。 結果的に得られた回路を少しずつ説明します。

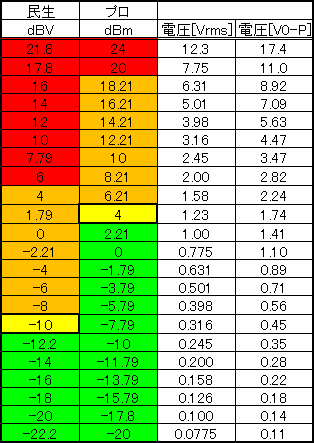

Fig:1 MOSFET出力電流帰還アンプ |

Fig:1に電流帰還,MOSFET出力を実現したシンプルな等価回路を示します。

入力段はバイポーラ・トランジスタです。Vbe電圧はダイオード接続したトランジスタによって得ています。

入力段のコレクタ出力をカレントミラーで折り返して出力段のMOSFETのゲートを駆動しています。

電流帰還アンプとしてはもっとも単純な形式と思います。

ただし,出力段のMOSFETはNchとPchを組み合わせた異極性SEPPですので,コンプリメンタリFETを選ぶ必要があります。

出力段素子の選択がこの回路のボトルネックとなります。

なぜなら,リニア増幅用のコンプリメンタリFETは品種が非常に限られており入手性がよろしくありません。

なにせ用途がオーディオアンプ用という限定的な市場なので,新規開発の高性能品もないし,競争が無いので価格面も不利です。

回路的なポイントはゲート・バイアス回路です。温度補償を出力段素子に合わせて的確に行う必要があります。

入力段,カレントミラー段の熱結合も確実に行う必要があります。

入力のバイアス電圧を作るI1,I2の作り方も工夫の余地があります。

以上のようなことを考慮して設計すればそれなりの特性が得られるでしょう。

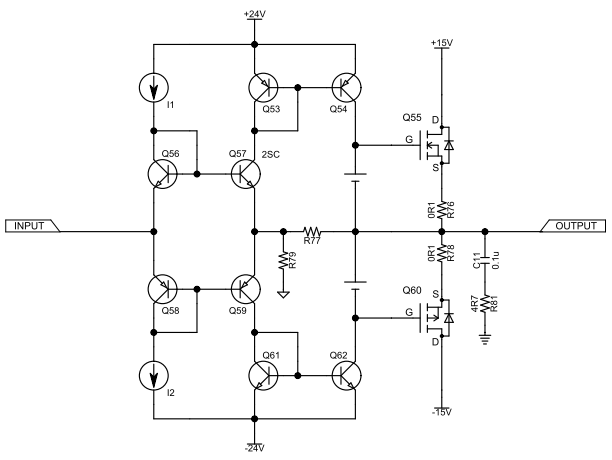

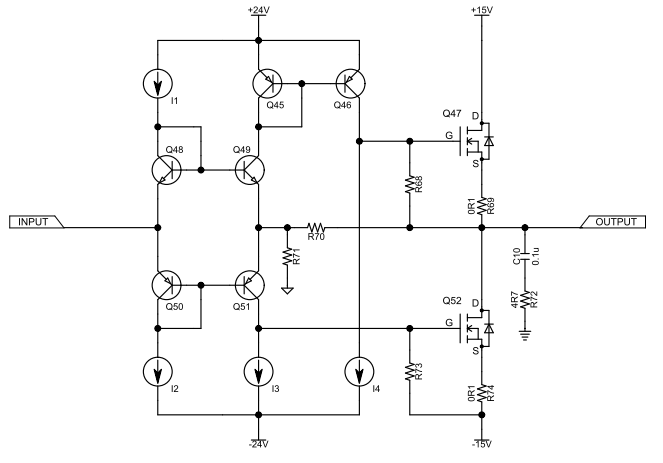

Fig:2 MOSFET出力電流帰還アンプ |

Fig:2に示した回路はさらにシンプルな2段構成としてみました。

初段を定電流負荷で受けて電流変化をIV抵抗(R102,R106)で電圧に戻し,出力段のMOSFETのゲートを駆動しています。

出力段はソース接地出力となっており,やはりコンプリメンタリ素子が必要になります。

ポイントはIVゲインです。IV抵抗の値が小さいと回路のゲインが小さくなり,オープンループゲインが下がります。

オープンループゲインが小さいと負帰還による歪み抑圧効果や,DC変動抑圧効果が少なくなるので,アンプとしての仕上がり特性が悪くなります。

かといって,IVゲインを高く(抵抗値を大きく)設定するとDC安定度に問題が出ててきます。

各トランジスタの温度ドリフトによってアイドリング電流が不安定となり,アイドリング電流を一定に保つことが難しくなります。

DC安定性の改善は熱結合を行うことによって軽減できますがI1〜I4の電流の不均衡がそのまま出力に現れるので完全な安定化には課題が多いです。

特にアンプが冷えている状態から電源投入後,想定するアイドリング電流に達するまでに数分かかってしまいます。

ターンオンドリフトといい,シリコン基板上にモノシリックに作られたICでも問題になることがあります。

回路全体の熱平衡が保たれるまで秒オーダーの速度で電流や電圧がドリフトしてしまいます。

大きな回路になると風の当て方や基板が水平か垂直かで電流や電圧が変化します。

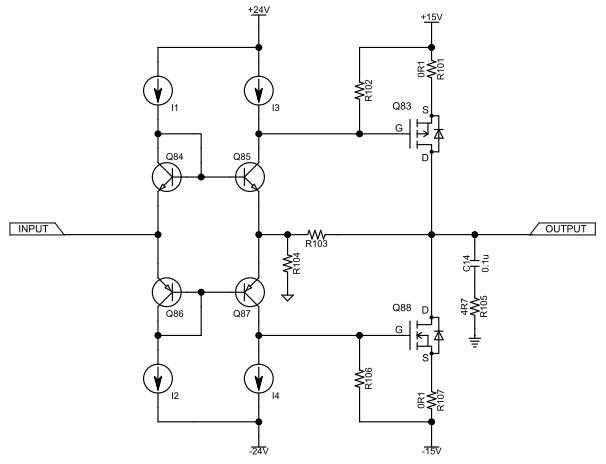

Fig:3 MOSFET出力電流帰還アンプ |

Fig:3はFig:1と同様のソースフォロワー出力ですが,Fig:2と同様のIV抵抗を使っています。

Fig:1に比べてオープンループゲインが低く,熱的に不安定になります。この特徴はFig:2と同じです。

出力段はコンプリメンタリ素子だという点もFig:1と同様なので,ある意味最も不幸な組み合わせと言えましょう。

Fig:1は上側回路と下側回路の電流ドリフトが両方増える方向であっても,ゲートバイアス電圧の生成回路が適切ならばアイドリング電流に変化はありません。

Fig:3では上側と下側の電流が両方とも増えるとアイドリング電流が増えてしまうという欠点があります。

したがって,アイドリング電流を安定化するためには冷えている状態から熱平衡状態に至るすべての瞬間ですべての素子の熱バランスを維持しなければなりません。

どだい無理な注文です・・・

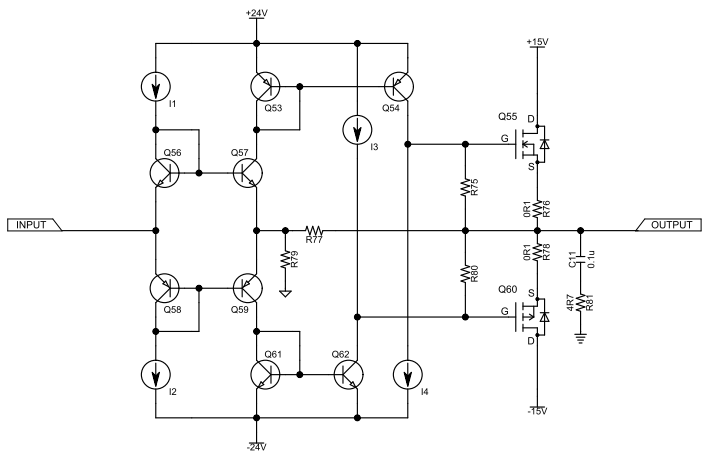

Fig:4 MOSFET出力電流帰還アンプ |

Fig:4はFig:2とFig:3を組み合わせた回路です。

この回路の一番の特徴は出力段のMOSFETが同極性のSEPPとなっている点です。

Fig:1のような異極性SEPPにおいてどちらかのFETの応答が遅い場合,立ち上がりの早い入力に対して貫通電流が流れることがあります。

負帰還アンプの帰還作用により遅いFETの動作を反対側のFETが補おうと作用するためです。

ちなみに負帰還によって発生する現象なので出力段無帰還アンプでは発生しません。

一般的にコンプリメンタリと言われるFET同士でもPchの応答はNchに比べて致命的に遅いです。

したがってMOSFET出力のSEPPアンプに立ち上がりの早い電圧を入力してはなりません。

恒久的に貫通電流を防ぐには入力にLPFを入れて立ち上がり(SR:スルーレート)を制限する必要があります。

電流を吐き出す上側のFETと電流を吸いこむ下側のFETの応答速度が一致していれば貫通電流は発生しません。

同極性のSEPPの強みはここにあります。速度が遅いPch素子に足を引っ張られることが無いので,Nch素子の性能を出し切ることができます。

つまり,進歩著しいのスイッチング用の高速・大電流に対応した新しいMOSFETを使うことができますので高速なアンプを実現することができます。

これが一番のメリットです。

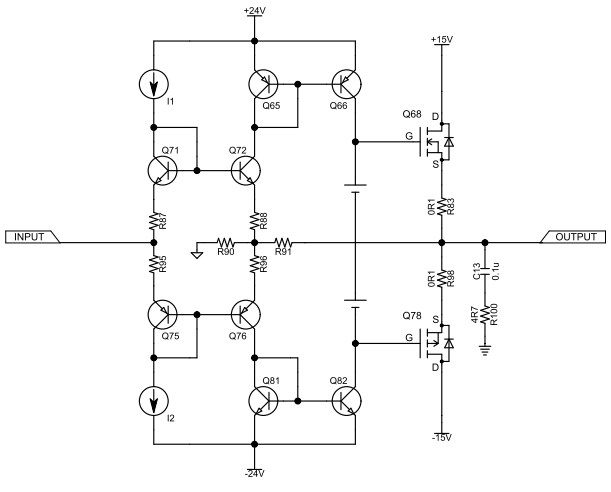

Fig:5 MOSFET出力電流帰還アンプ |

Fig:5はFig:1の回路を実現するにあたって障害となる温度安定性を改善するアイディアを示しています。

この回路においてQ71/Q72および,Q75/Q76にペアトランジスタを使用し,4つのトランジスタを完全に熱結合すると熱的に安定になります。

しかしそれでも電源投入直後の過渡的な状況においては,発熱量の差から温度ドリフトが発生します。

温度ドリフトはDCオフセットを発生させると共にアイドリング電流の変動となって現れます。

そこで,Fig:5のように初段トランジスタのエミッタに抵抗(R87,R88,R95,R96)を入れると温度安定性が高まります。

温度ドリフトはVbeの温度変動が原因なので,Vbeの変動に対して充分大きな電圧(0.5V〜1.0V程度)を発生する抵抗を入れると,Vbeの変動がマスクされます。

結果的にVbeのバラつきや温度変動に対してロバストな回路となります。

同様の効果を期待してカレントミラーのエミッタに抵抗を挿入する例はよく見受けられます。

デメリットとしてはトランスインピーダンスの低下と帯域制限効果が挙げられます。

入力にシリーズに抵抗が入ることで入力容量によってLPFを構成し,帯域制限がかかってしまいます。

帰還回路側は帰還信号の位相が回ることになりますのでより注意が必要です。

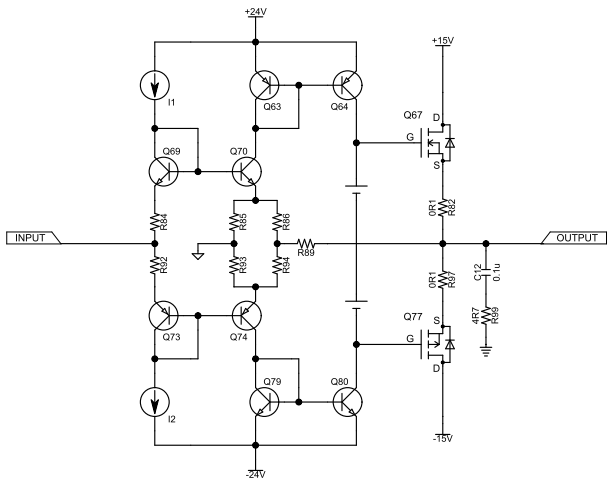

Fig:6 MOSFET出力電流帰還アンプ |

Fig:6はFig:5で発生したトランスインピーダンスの低下と帰還回路側の帯域制限効果を同時に緩和する回路です。

帰還回路の抵抗をT型(十字)からπ型(ロの字)に変換しました。

これらの抵抗(R85,R86,R93,R94)がDCの誤差吸収と帰還回路網を兼用するので,帰還回路の帯域を制限することなく,Vbeの変動に強い回路とすることができます。

ただし,このままではトランジスタの入力容量に大小によって上下のバランスが崩れてしまいます(特に立ち上がりの速い信号)ので,

Q70とQ74のエミッタ同士を小容量のコンデンサで結合して素直な立ち上がりを得ています。

Q69とQ73のエミッタ同士もコンデンサで結合するとよいが,それぞれコンデンサでグランドに落としてやることで入力信号に対するLPFとなり,回路の安定化に貢献します。

以上のことは非常に簡単なことですがこのような回路を見たことがありません。

先例があるかどうか気になるところです。

2-2-2:電流帰還アンプの入力段回路

電流帰還アンプの初段はエミッタ・フォロアを使うことから初段トランジスタを動作させるには工夫が必要です。 0.6V〜0.7Vあるベース・エミッタ間電圧(Vbe)をどのように補償するのかがテーマとなります。

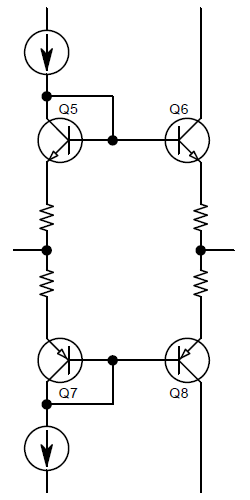

Fig:2-2-2-1 電流帰還アンプ初段バイアス回路 |

Fig:2-2-2-1はダイオード接続したトランジスタに定電流を流して初段のVbeを補償するもっとも基本的な回路です。

Q5/Q6とQ7/Q8に同じ特性のトランジスタを使うことによってオフセット電圧とその温度ドリフトを小さく抑えることができます。

ディスクリート部品で作るならば4つのトランジスタを熱結合させることによって温度ドリフトがキャンセルされます。

さらにエミッタに抵抗を入れることによって安定度を向上させることができます。

この回路の欠点はダイオード接続したQ5/Q7のエミッタ電流がQ6/Q8のベース電流に食われる分だけ減少してしまう点です。

Q6/Q8のhfeに誤差があると上下二つの定電流源がマッチングしていても誤差電流が発生してしまいます。

すべての動作領域・温度範囲でhfeが完全に一致することはないので必ず誤差が残ります。

この誤差は入力バイアス電流として表れますからDCアンプの初段としては使えません。

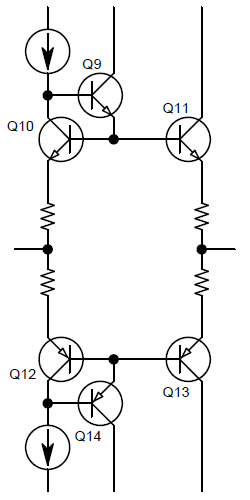

Fig:2-2-2-2 電流帰還アンプ初段バイアス回路 |

Fig:2-2-2-2はQ11/Q13のhfe誤差を吸収するために2石追加しています。Q9/Q14がQ11/Q13のベース電流を補償します。

前述の誤差電流は1/hfeに圧縮されます。カレントミラーでよく使われる手法です。

温度変化などでhfeが変動しても誤差電流が発生しにくくなります。

最大の利点は入力に流れるバイアス電流をとても小さく抑え込める点です。

バイポーラ・トランジスタによるDCアンプは入力段のベース電流キャンセルが必須になりますが,この回路ならばうまく抑え込めます。

また,ダーリントン接続になっていることからhfeが飛躍的に増加し,入力インピーダンスが上昇します。

温特もよいです。Q10のVbeはQ11によって補償され,Q12のVbeはQ13によって補償されます。PNP同士,NPN同士なので温度特性もよく一致していますからドリフトがキャンセルされます

実際に作ってみたところ入力バイアス電流は0.1uA以下に追い込むことができ,オフセット電圧の温度ドリフトも10mV以下でした。

なお,Q9/Q14のコレクタ電流は微小です。コレクタ電流が小さいとトランジスタの特性が悪くなりますので,バイアス電流を流した方がよいです。

具体的にはQ9/Q14のエミッタ間に抵抗を挿入します。

このパワーアンプは電流帰還アンプですがこの回路のおかげでカップリングコンデンサを追放し,DCアンプ化することができました。

さらに先に紹介したエミッタ抵抗をT型(十字)からπ型(ロの字)に変換するというアイディアも合わせることで優れたDC安定性を実現しています。

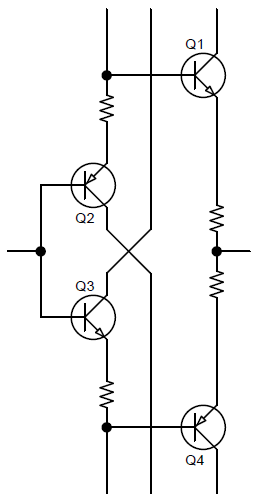

Fig:2-2-2-3 電流帰還アンプ初段バイアス回路 |

Fig:2-2-2-4 電流帰還アンプ初段バイアス回路 |

Fig:2-2-2-3はダイヤモンド・バッファ回路と言われる有名な回路です。シンプルで人気のある回路です説明しておきます。

NPNトランジスタとPNPトランジスタを相補的に使いお互いのVbeを補償しています。

シンプルに高機能を実現できるので自作アンプではよく使われる形式です。

ダーリントン接続なのでhfeの増加も期待できます。

この回路は大きな欠点があります。VbeをNPNとPNPが相補的に補償している点です。

つまり,Q2(PNP)のVbeをQ1(NPN)のVbeが打ち消しているのです。

PNPトランジスタとNPNトランジスタは例えコンプリメンタリペアと称していても特性は異なります。

VCE-IC特性に違いがありますし,同じコレクタ電流でもVbe電圧は一致しませんので必ずオフセットが発生します。

仮にオフセット調整を行ったとしても,PNPとNPNでは温度特性が異なりますので温度が変化すればオフセットが変化します。

したがって,ダイヤモンド回路は本質的にオフセットをゼロにすることはできません。

また,入力バイアス電流もゼロにはなりません。Q2/Q3のhfeが奇跡的に一致していれば,いい具合にキャンセルしますが,hfeは一定ではありません。

つまりDC安定度が悪く,入力のカップリング・コンデンサも必須になりますので,DCアンプにはできません。

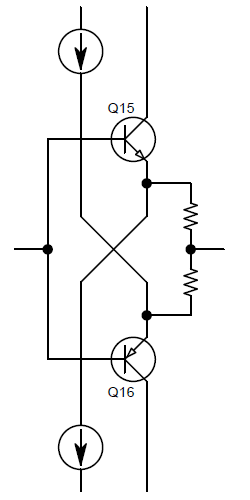

Fig:2-2-2-4はさらにシンプルにした回路です。エミッタに抵抗を入れることでVbeを作り出しています。

定電流源にはトランジスタに流れる電流とVbe/抵抗値に相当する電流を加算した電流が流れます。

Q15と定電流源のトランジスタ(絵には表れていない)を熱結合し温度特性を一致させるとDC安定度の高い回路にすることができます。

実はこの回路,アキュフェーズのアンプで使われています。巧妙な回路です。

ただし,入力バイアス電流については状況は変わらず,DCアンプにはできません。

入力にDCが流れるアンプのカップリング・コンデンサを省いて直接ボリュームを入れるとボリューム位置によってオフセットが変動するアンプになります。

また,DCが流れ続けることによりボリュームの抵抗体が損傷することもあります。

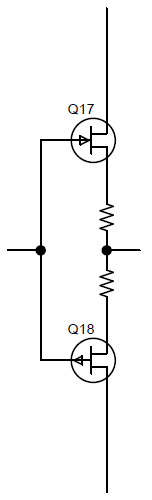

Fig:2-2-2-5 電流帰還アンプ初段バイアス回路 |

Fig:2-2-2-6 電流帰還アンプ初段バイアス回路 |

Fig2-2-2-5はFET入力にした場合です。DCアンプはFET入力だろって人はこうなります。

バカにしているわけではなく立派な実用回路です。

最もシンプルに電流帰還アンプを成立させることができます。

回路がシンプルなので作りやすいですし,シンプルなだけに動作上の素性も悪くない,つまり真空管アンプ的な素直な回路です。

トランジスタ・アンプはどうしても付随回路がゴテゴテと追加されて複雑化してしまいますが,

J-FETのデプレッション特性をうまく使うとこのようにシンプルにすることができます。

オフセット調整はソース抵抗値で行います。

Fig:2-2-2-6はバイポーラ・トランジスタを追加したパターンです。

FETだけだとGmが低く,出力インピーダンスも高いので,電流帰還回路としては不完全です。

そこでバイポーラ・トランジスタを追加するとGmが高くなり,出力インピーダンスも低くなります。

入力バイアス電流はほとんど流れませんのでDCアンプとすることもできます。

ただし,温度特性の異なる素子を使っている以上,オフセット電圧の温度ドリフトは覚悟しなければなりません。

オフセット補正はQ19/Q22のソースに一定電流を注入もしくは吸出しする回路を追加すると可能になります。

以上何種類か紹介しましたが,PNP/NPN混成のダイヤモンド・バッファ回路,FETを使った上下対象回路はDCアンプには向きません。 もちろん対策は考えられます。例えばオフセット電圧の温度ドリフトの問題はDCサーボを追加すれば抑え込めますがDCアンプではなくなります。 入力バイアス電流の問題はDC特性の優れたバッファーを前置段として加えれば解決できますが回路規模が大きくなってしまいます。

わたしとしてはPNPの温特はPNPで補正する。つまりPNPのVbeはPNPのVbeで補う。逆(NPN)も然り。 といった具合にまずい部分をうまくキャンセルできる回路がいいと思っています。

Fig:2-2-2-2はDCサーボも不要で,入力バイアスも極小に調整できます。総合的に最もシンプルで高機能と考えています。 電流帰還DCアンプはこの初段回路のおかげで成立していると言えます。

Fig:2-2-2-2回路のDC特性の優秀さは実際に組み立てたアンプで証明されています。 入力バイアス電流は0.1uA以下とバイアス電流キャンセル回路を内蔵したバイポーラ入力のオペアンプと同程度, 出力オフセット電圧は10mV以下とパワーアンプとしては優秀な値です。どちらも温度に関係なく電源ON直後から常に安定しています。

2-3:高速 高安定 電流帰還 MOSFET DCアンプ

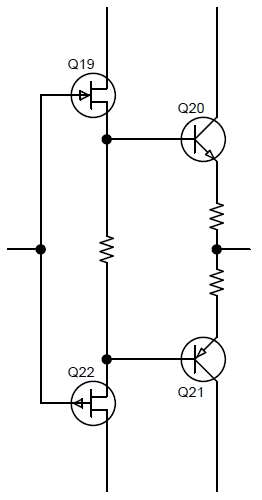

Fig:7 MOSFET出力電流帰還DCアンプ実用回路

Fig:7はFig:6を基本として,初段および,カレントミラーのVbeバラつき吸収,ベース電流補償,定電流回路,電源リップルフィルタ,保護回路,オフセット調整回路を搭載した実用回路図です。

図中の電圧・電流は設計値を示していますが,実測でも概ねこの通りになります。 使用しているトランジスタ,MOSFETについては別項に記載しています。

2-3-1:入力段について

2-2-2で説明した通り,入力は標準的な電流帰還アンプの構成をとっています。 バイポーラ・トランジスタのベースに信号を入力し,出力からエミッタに電流帰還を戻しています。

入力部のバイポーラ・トランジスタはVbe電圧分のバイアスを与える必要があります。 そのために入力にバイアス回路が入るのが電流帰還アンプの特徴ともいえます。 2-2-2に記す通り初段のバイアスを如何に料理するかが電流帰還アンプの面白い部分です。

通常はダイオード接続したトランジスタを定電流で駆動して初段のトランジスタにマッチしたVbeを発生させます。 ところが,精密な定電流源でバイアス用ダイオードをドライブしても初段のトランジスタのhfeが異なればベース電流として奪われる電流の分だけ誤差がでてしまいます。 hfeは当然のごとく変動するのでオフセットやドリフトが発生します。

この誤差を取り除き,入力バイアス電流のドリフトを最小限に抑える為,ベース電流補償用のトランジスタ(Q11/Q19)を追加しました。

ところでベース電流補償用のトランジスタを追加すると面白いことに回路トポロジが変わって見えてきます。

まず信号が入力されるトランジスタがベース接地・エミッタ入力の増幅回路に見えます。

定電流負荷から湧き出した電流をエミッターフォロアでバッファして入力段のトランジスタを駆動するという回路に見えます。

目を凝らし眺め続けると,局部帰還がかかった,ベース接地エミッタ入力のダーリントン接続エミフォロ出力という回路に見えてくるから不思議です。

ベース接地もエミフォロもどちらも高速な回路なのでこの回路が高速に動くのは合点がいきます。

入力トランジスタのエミッタにはトランスインピーダンスの低下を伴わずにDC安定度を大幅に向上させ, しかも入力の帯域制限を行えるという一石三鳥の効果を実現できるような形でエミッタ抵抗を挿入しています。 この回路形式はディスクリートだからこそ実現可能です。オペアンプを使った回路では実現不能です。

入力段のエミッタに入るコンデンサ(C7)は速いパルスに対する応答をよくするために必要です。 入力側のコンデンサ(C5)はC7に対応して電源投入時にMOSFETに大電流が流れるのを防止します。 もう一つ入力側のコンデンサ(C6/C8)は入力信号をLPFしてあまりに立ち上がりの速い信号が入らないように制限する効果があります。

2-3-2:定電流源について

初段を定電流駆動する部分は上下から供給される電流のバランスが重要になるため同じ電流源を使ってカレントミラーで折り返しました。 このカレントミラーも電流誤差を減らすためにベース電流補償トランジスタ(Q8/Q21)を追加しています。

定電流回路は単純化のためと確実な立ち上がりを期待して定電流ダイオード(CRD)としました。 CRDは全ての回路電流の大元となる為,実測してL/Rのマッチングを取りました。

CRDは10V程度の電圧をかけると安定してきます。また動作抵抗がそれほど高くないので電源は安定化しておく必要があります。 電源電圧は±30V以下を予定しており定電流ダイオードにはかかる電圧は最大で60Vとなりますが,CRDの耐圧はもっと高いので安心です。 電流値は1mAを使うので損失は少なく発熱も少ないので心配ありません。

2-3-3:駆動部・出力段について

初段で電圧・電流変換された信号は電流によって伝送されます。

カレントミラーにもベース電流補償トランジスタ(Q9/Q22)とVbeの誤差を吸収する抵抗(R6/R8/R29/R31)を追加しました。 ベース電流の誤差をなくすことで動作電流の誤差が減りますので,トランジスタの選別は必要ありません。 また,電流バランスが取れると熱的な安定性もよくなるという効果も期待できます。 もう一つ,抵抗を追加するとカレントミラー回路から発生するノイズを抑制する効果もあります。ここも一石三鳥です。

余談ですが,ベース電流補償トランジスタにはアイドリング電流をそれなりに流しておくと様々なメリットがあります。 トランジスタはアイドリング電流を流すことによりhfeが大きくなり,動作電流による非線形性が小さくなり,ftが上昇して応答が早くなります。 そのため抵抗(R4/R7/R16/R27/R30)を追加して1mA程度の電流が流れるようにしてあります。

出力段はバイアス回路によってバイアス電圧を与えられます。

バイアス回路はコンデンサ(C4)でバイパスされます。出力段のFETのゲート間を結ぶことで二つのFETがより密な動作となります。 そのためにはゲート容量よりも十分に大きな容量を選んでおく必要があります。 同時にVbeマルチプライアを使ったバイアス回路がL性の応答を示すのでそれを打ち消す効果もあります。

バイアス回路のツエナーダイオード(D7)は温度補償特性の調整用です。温度係数ゼロの定電圧源として期待しています。 後から知ったのですがルネサスのLLシリーズは流す電流量によって温度特性が変化しますので今回の用途にはちょうどよかったです。

MOSFETの温度補償はトランジスタ(Q15)によって行われます。Vbeマルチプライアという回路構成です。 VRのワイパがオープンとなった時に出力段に過大な電流が流れることを防止するためにベース側にVRを挿入しています。

2-3-4:各部の電流について

定電流ダイオードは1mAとして,初段バイアス部は1mA,初段は10mA,カレントミラーは10mAで折り返してMOSFETを直接駆動しています。 出力段は100mA〜200mAのアイドリング電流を流します。

初段に10mAという電流は破格です。FETを使うなら数mA,バイポーラ・トランジスタの場合1mA以下の場合もあります。 オペアンプやパワーアンプICなどは間違いなく1mA以下です。真空管アンプでは電流を流せば流すほど音が太くなるみたいな表現が言われることがありますが,トランジスタ・アンプではどうでしょう。 電流が増えると相対的にショット・ノイズが減ります。また,抵抗値が下がりますので熱雑音も減ります。1/fノイズもおそらく減るでしょう。 こういったSNの向上が出音に良い効果をもたらすかもしれません。

全体的に電流を多く流すことで容量を素早く充放電し高速化が期待できます。 この回路の応答はMOSFETの入力容量とカレントミラーの折り返し電流が支配的と考えています。 駆動電流をもっと流せばさらに高速に動作しますが,発熱も増える為,控えています。

ドライブ電流:10mA,ゲート電圧:5V,ゲート電荷:500pFの条件だと2500pC/10mAなので,250nsecで電荷の抜き差しができます。 これがスルーレートを決める条件です。ちなみにゲートに5V与えると10Aは流れます。

2-3-5:調整のしくみについて

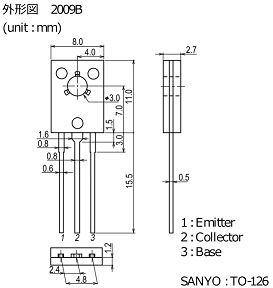

VR1によって出力段のアイドリング電流を決めます。 アイドリング電流を安定化するためには温度補償用のトランジスタ(Q15)を出力のMOSFETと熱結合をしっかり行うことが基本です。 そのため,ヒートシンクにネジ止めできるTO-126タイプのトランジスタ2SC3423を使いました。

バイアス電圧を最小に設定した状態でアンプの電源を投入し,徐々に電流を増やしながら時間をかけて最終的なバイアス電流に調整します。 その後,一旦アンプの電源を切りアンプが十分に冷えた状態で電源を再投入します。アイドリング電流が不本意に増加しなければOKです。

アイドリング電流の安定性は初段トランジスタおよびカレントミラーの熱結合の状態によっても変化します。 初段トランジスタにより大きな熱容量を持たせて周囲よりも温度上昇が遅くなるようにすると電源投入直後にアイドリング電流が増加する現象を防ぐことができます。

VR2によってDCオフセット調整を行います。出力端子で10mV以下まで楽勝で追い込めます。 しかし何らかのヒステリシス効果があるようで1mV以下に追い込むのは難しかったです。 電源投入後のドリフトも僅少で常に数mV以下に収まります。 VR2を動かすとアイドリング電流がやや変化するのでVR1によって補正をおこないます。

VR3によって入力バイアス電流の調整が可能です。 入力バイアス電流が十分に少なければDC結合が可能になり,DCアンプとして使用できるようになります。 DC結合で不必要に直流電流が流れていると音量調整ボリュームを操作した時にザザザというノイズがでたり,入力セレクターを切り替えた際にバチというノイズがでます。 それだけでなく,カーボンを使ったボリュームに不可逆なダメージを与えることもあります。

どんなに回路と工作を工夫しても多少ドリフトするので,よく使用する室温でバイアス電流を調整します。 入力には何も接続しません。バイアス電流はR20(10kΩ)に流れます。入力端子の電圧を1mV以下に追い込むことができます。 10kΩですので,1mVで0.1uAと換算できます。この程度の電流ならばDC結合しても問題ありません。

これで電流帰還アンプながらDCアンプとすることができました。 これは他には例のないことです。

2021/11/29:と思っていたら新興メーカーからダイヤモンドバッファを使ったDCアンプが売られています。 オフセット電圧がどの程度か,温度ドリフトしないのか,入力電流は十分小さくなっているのか気になるところです。 ちなみに,このアンプは電流帰還のDCアンプという点だけではなく,ゲインが5.3倍と低く,残留ノイズが10uVと小さく,定格出力は20Wと小さい。 つまり,このアンプと非常によく似たコンセプトのアンプです。このような真面目なアンプがどんどん増えてくれると嬉しいです。

2-3-6:保護回路について

思わぬ大電流によりFETが破壊されると大きなDC電圧が発生してスピーカーを破壊してしまいます。 そんな事故を防ぐために出力段には電流リミッタを組み込みました。

0.1ohmの検出抵抗により,トランジスタのVbe電圧に応じて高温では5A〜6A程度,低温では7A〜8A程度の電流でリミッタが働きます。 FETのゲート電圧をクリップさせてFETに流れる電流を制限します。 先に計算例を示しましたが,スピーカーをドライブする条件とちょうどマッチする数字と考えています。

ループゲインが急速に減少する方向のリミッタであり,かつリミット状態からの復帰も高速にしているため誤動作しにくいと思います。

2-3-7:パワーアンプのゲイン設定について

昔からの伝統なのか,パワーアンプというとゲインを20倍(26dB)に設定しているアンプが多いです。 20倍のゲインを全開で使うと一体何ワットの電力になるのでしょうか。

民生機器の出力レベルを-10dBV(0.316V)として仮に最大レベルが基準よりも+16dB大きい+6dBV(2.0V)だとします。 すると,20倍のゲインでは40Vの出力電圧となり,8Ω負荷では200Wの電力となります。

さて,200Wも出力はいらないので,もっとゲインを下げていいことになります。 では実際のところ,どれだけのゲインが必要なのでしょうか。

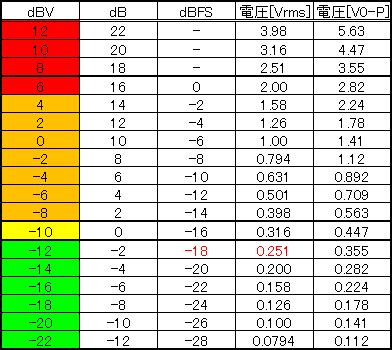

|

Table:民生機器の音声信号レベル Table:業務用機器の音声信号レベル |

民生機器の最大出力レベルは+6dBVとしている製品が多いようですので,グーグル氏問い合わせたところ 「"-10dBV" "-16dBFS"」 を基準とすることが多いようです。

地デジでは「出力レベル. : 250mVrms±3dB. (フルスケールレベルから −18dBのレベルに対して)」という規定があるようです。

引用:電波産業会:"www.arib.or.jp/english/html/overview/doc/2-STD-B30v1_3.pdf"

250mVrmsは-12dBVであり「-12dBV / -18dBFS」となり,「-10dBV / -16dBFS」と一致します。

JEITA CP-1301Aでは以下のようになっています。

基準入力レベル:アナログ入力:0.5Vrms,デジタル入力:IEC61606-1に規定する-12dBFSの信号レベルを用いる。

最大入力レベル:アナログ入力:2.0Vrms,デジタル入力:IEC61606-1に規定する0dBFSの基準フルスケール信号レベルを用いる。

0.5Vrmsは-6dBVなので「-6dBV / -12dBFS」となり「-10dBV / -16dBFS」と一致します。

偶然か必然か,3つの数字が一致しましたので「これでいいのだ」という自信が深まります。

昔の放送機器は-20dBu(100mVくらい)だったこともあるらしいです。 古いCDプレーヤーなどは-10dBV(-20dBFS)という基準だったり,もっといい加減に作られていたこともあるようです。 まあ,ソースは自作DACなのでどうにでもなりますが。。

「"-10dBV" "-16dBFS"」という基準を右の上に表を示しました。民生機器では基準はどうあれ,最大出力レベルは+6dBVとなります。 アナログ機器では+6dBV以上突っ込んでも何とかなりますが,デジタル機器は対応できません。

さらにここで注意が必要なのは,ここでいう信号レベルというのは正弦波の実効値であるという点です。 パワーアンプはピーク電圧を充分に出力する必要がありますので,√2倍した電圧が0-P(ゼロtoピーク)として必要になります。

一方,プロの録音環境ではどうなのかもう一度グーグル氏尋ねたところ 「"0VU" "-16dBFS"」 を基準とすることが多いようです。0VU=+4dBmです。

下の表にプロ機と民生機のレベルを比較したダイアグラムを示しました。 プロ機で最大で+20dBmまで考えるとなんと11V0-Pもの電圧が必要になります。 プロ用機器の内部回路の電源電圧が±15V以上必要である理由はここにありました。

さて話を戻すと・・・アンプの必要ゲインの話でした。

民生機器の最大出力電圧は+6dBVであり,ピーク電圧は2.8V0-Pなので,この入力に対して出力10W(12.6V0-P)を得るのならば,ゲインは4.5倍必要となります。 実際,110dBもの音圧を浴びる気はないので,ゲインは4倍としました。 なお,R14をゼロΩとするとゲイン2倍,220Ωとするとゲイン4倍,330Ωとするとゲイン5倍となります。

実際出来上がったアンプで視聴すると,これ以上音を大きくしたくないと思うレベルでもアッテネータは-20dBの位置にあります。 つまり余剰ゲインが20dBもあるので仮に仕上がりゲインを2倍としても十分実用に耐えることになります。むしろゲイン0dB,つまり増幅する必要も感じません。 ただし,スピーカーは超高能率(103dB/m)のJBL D130ですので,90dB/m以下のスピーカーでは不足するかもしれません。

巷のアンプはゲイン過剰でSNも悪くよいことはありません。 特に非常に能率が高いホーン・スピーカーには低ゲインで低ノイズのアンプを使うべきです。 そうしないと音楽ではなく「サー」というアンプの残留ノイズを鑑賞することになります。 残留ノイズが少ないアンプがほとんどないことからわかる通り,ホーン・スピーカーから「サー」というノイズが出るのはある意味当たり前なのですが,これではハイレゾの時代には対応できません。

2-3-8:おまけ:同極性SEPPの実際

Fig:9

Fig:9はFig:4を基本とした非常に高速なDCアンプですが,アイドリング電流の安定化に課題が残り実用化を見送りました。 具体的に困った現象とは,電源投入後のターンオン・ドリフトによりアイドリング電流が数Aに達してしまうという現象です。 出力段のみ電源投入を1分ほど遅らせればこの現象を防ぐことができます。しかしそんなに気が長くないので・・・

上側の回路はカレントミラーで折り返して定電流負荷に信号電流を供給します。 出力のNch MOSFETのゲートには負荷としてIV抵抗を接続してあります。信号電流はこの抵抗でIV変換されてFETを電圧駆動します。

下側の回路は電流帰還がかかる入力トランジスタのコレクタ出力を定電流で受けつつ直接FETを駆動しています。

つまり,上側は1段増幅+カレントミラーでドライブ,下側は1段増幅で直接ドライブということになります。

全体のゲインは初段のトランスインピーダンスと負荷のIV抵抗で決まります。 IV抵抗を大きくすればゲインを上げることが可能だが,DC安定性や動作安定性を考慮するとせいぜい47kΩまででしょう。

上下共にNch FETを使用することで立ち上がりと立下りの速度を最速の条件で一致させることができることが特徴で強烈なスルーレート(100V/us)が出ます。

2-4:トランジスタの選定

2-4-1:MOS FETの選定

オーディオ用のパワーMOSFETと言えば2SK135/2SJ50が始祖に当たると思います。 当時の状況は詳しくないのですが,自作記事でもよく登場しているので使いやすい定番の石ということでしょう。 缶パッケージのMOSFETというだけで珍重されていてモールドパッケージの2SK1058/2SJ162は入手可能なようです。 ラテラル構造(横型)のMOSFETはリニアアンプには適していると言われているようです。 しかし,最新のトレンチ構造(縦型)の方が素子てしての性能は高くスイッチングデバイスとして重視されるON抵抗は低くなります。 ところが用途がリニアアンプとなればON抵抗を論じることが無意味であり,静特性はもちろんですが,動特性に関わるゲート容量やDC安定度に関わる温度特性が重要になるのではないでしょうか。

出力段のMOSFETは入力容量が小さいほど少ない電流で高速に駆動することができます。一方,ON抵抗が小さければ飽和電圧が小さく,電源を有効に使えます。 一般的に入力容量が大きければ素子も大きく,ON抵抗も小さくなり大きな電流に耐えます。そして同時にゲインに相当するGmも大きくなります。 入力容量とON抵抗は反比例の関係にあるので,より少ない容量でより低いON抵抗を実現できることがMOSFETの性能の指標となります。

耐圧が低い方が良い性能を示しますが,耐圧が低いということは構造が微細なため破壊しやすいことを意味します。 出力段のFETがショートモードで故障するとスピーカーを壊す可能性があるため耐圧は50V以上を目安にしています。 電流容量は10Aを目安とし,入力容量は500pF以下を目安として調査しました。

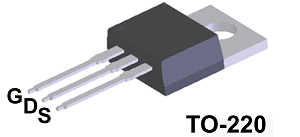

各社のデータシートを比較のうえ最終的にヒットしたのがSTマイクロのSTP16NF06Lです。

VDSSが60[V],IDは16[A]と手ごろでオン抵抗は0.07[ohm]typと低く,入力容量は345p[F]ととても小さく,ゲート電荷も7.3n[C]と少ないです。 許容損失は45[W]です。仕様書の用途にも「AUDIO AMPLIFIERS」と書いてあり,リニアリティも良さそうなので使ってみることにしました。

MOSFETはここ10年での進化が著しく現在の各社ラインナップから近い定格のモノを抽出してみました。 またオーディオ用として有名な国産のMOSFETと比較してみました。これらはもはや古典デバイスの部類に入ります。

| 項目 | 記号 | 2SK135 | 2SK405 | 2SK1529 | 2SK2554 | STP16NF06L | TK30E06N1 | FQP13N06 | IRLB8721PBF | IRLZ14PBF | PSMN022-30PL |

| VDS | [V] | 160 | 160 | 180 | 60 | 60 | 60 | 60 | 30 | 60 | 30 |

| ID | [A] | 7 | 8 | 10 | 75 | 16 | 43 | 13.6 | 62 | 10 | 30 |

| PC | [W] | 100 | 100 | 120 | 150 | 45 | 53 | 45 | 65 | 43 | 41 |

| Ciss | p[F] | 600 | 430 | 700 | 7700 | 345 | 1050 | 270 | 1077 | 400 | 447 |

| Yfs | [S] | 1 | 2 | 4 | 80 | 17 | - | 7 | 35 | 3.5 | 17 |

| Qg | n[C] | - | - | - | - | 7.3 | 16 | 4.8 | 7.6 | 8.4 | 4.4 |

| RDS | m[ohm] | - | - | - | 4.5 | 70 | 12.2 | 88 | 6.5 | 200 | 19 |

| PKG | - | TO-3 | TO-3P | TO-3P | TO-3P | TO-220 | TO-220 | TO-220 | TO-220 | TO-220 | TO-220 |

| MFR | - | Hitachi | Toshiba | Toshiba | Renesas | STmicro | Toshiba | Fairchild | IRF | Vishay | NXP |

| コメント | - | オーディオ用 横型MOSFET元祖 |

オーディオ用 | オーディオ用 | UHC MOS FET | 今回選定 | 東芝の現行 | 新しいもの | 新しいもの | 新しいもの | 新しいもの |

Nch MOSFETは手ごろなものが見つかりましたがPchはかなり悲しい状況です。 Pch MOSFETはNchと比較して入力容量が倍程度大きく,さらにON抵抗も高くなります。 STP16NF06Lとコンプリメンタリ・ペアとして使える品種はありませんでした。

それでもあきらめなかった理由はリニア増幅用のおじいちゃん達がペアで1000円以上するのに対しスイッチング用のヤンチャな若者たちは1ドル以下だからです。

選定方法を変えて,まず手ごろなPchを見つけて,それに見合うNchを探すという手順で選びました。 一晩探して目を付けたのがフェアチャイルドの石「FQP17P06」と「FQP30N06」です。

Nchの電流容量がオーバースペックになるのは致し方ありません。 この二つのペアが秀逸な点は低電流時のゲート電圧がほぼ一致する点です。 入力容量もかなり近いです。Yfsが一致していないように見えますが測定条件が異なります。 1A程度の領域では結構マッチしています。

FQP17P06は2SJ50や2SJ115よりも入力容量が小さいにもかかわらず電流容量は倍以上あります。Gmは4倍もあります。 UHC MOSFETよりも値段が手ごろで入力容量が少ないのでドライブしやすく,古典的な横型(ラテラル)MOSFETの代替えとして丁度良いと思います。

著名なオーディオ用コンプリメンタリ・ペア・パワーMOS FETを並べてみました。 こう眺めてみると10年ほど前に登場してオーディオ用として騒がれた「UHC MOSFET」は入力容量が巨大で完全に時代遅れに見えます。

「FQP17P06」はよくできており,オーディオ用として定番で有名アンプにも使われている「2SJ200」に比べると入力容量は半分程度です。 耐圧が60Vと低いこと,小型なTO-220パッケージであることから出力はせいぜい50Wまで,100W級の大出力アンプには使えません。

| 項目 | 単位 | 2SK135 | 2SJ50 | 2SK405 | 2SJ115 | 2SK1529 | 2SJ200 | 2SK3497 | 2SJ618 | 2SK2955 | 2SJ554 | 2SK3163 | 2SJ555 | 2SK2232 | 2SJ334 | FQP30N06 | FQP17P06 |

| MFR | - | Hitachi | Renesas | Toshiba | Toshiba | Renesas | Renesas | Toshiba | Fairchild | ||||||||

| 極性 | - | N | P | N | P | N | P | N | P | N | P | N | P | N | P | N | P |

| VDS | V | 160 | -160 | 160 | -160 | 180 | -180 | 180 | -180 | 60 | -60 | 60 | -60 | 60 | -60 | 60 | -60 |

| ID | A | 7 | -7 | 8 | -8 | 10 | -10 | 10 | -10 | 45 | -45 | 75 | -60 | 25 | -30 | 30 | -17 |

| PC | W | 100 | 100 | 100 | 100 | 120 | 120 | 130 | 130 | 100 | 100 | 110 | 125 | 35 | 45 | 79 | 79 |

| Ciss | pF | 600 | 900 | 430 | 800 | 700 | 1300 | 2400 | 2300 | 2200 | 2500 | 7100 | 4100 | 1000 | 3300 | 725 | 690 |

| Yfs | S | 1 | 1 | 2 | 2 | 4 | 4 | 12 | 12 | 40 | 30 | 80 | 45 | 16 | 23 | 16 | 9.3 |

| Qg | nC | - | - | - | - | - | - | - | - | - | - | 125 | - | 38 | 110 | 19 | 21 |

| RDS | mΩ | - | - | - | - | - | - | - | - | 10 | 28 | 6 | 17 | 36 | 29 | 40 | 120 |

| PKG | - | TO-3 | TO-3P | TO-3P | TO-3P | TO-3P | TO-3P | TO-220 | TO-220 | ||||||||

秋月で手に入る東芝の2SK2232と2SJ334を追加しました。DC特性はよく一致しています。 しかしPchの入力容量が3300pFと巨大なので,動特性はあまりバランスしないと思われます。

巷ではFQA36P15とFQA28N15の組み合わせがオーディオ・アンプ用(Accuphaseが採用)として使われています。 2SK3497と2SJ618の代用といった位置づけでしょうか。入力容量がアンバランスなので私ならFQA46N15を使うかもしれません。

FQA36P15とFQA46N15は100Wクラスのアンプにはちょうど良いです。パラにしなくてもパッケージが大きいので安心して使えます。

| 項目 | 単位 | FQP30N06 | FQP17P06 | FQA28N15 | FQA36P15 | FQA46N15 |

| MFR | - | Fairchild | ||||

| 極性 | - | N | P | N | P | N |

| VDS | V | 60 | -60 | 150 | -150 | 150 |

| ID | A | 30 | -17 | 33 | -36 | 50 |

| PC | W | 79 | 79 | 227 | 294 | 250 |

| Ciss | pF | 725 | 690 | 1250 | 2550 | 2500 |

| Yfs | S | 16 | 9.3 | 20 | 19.5 | 36 |

| Qg | nC | 19 | 21 | 40 | 81 | 85 |

| RDS | mΩ | 40 | 120 | 67 | 76 | 33 |

| PKG | - | TO-220 | TO-3P | |||

最近はSiC MOSFETが話題ですが,あれは高耐圧向けの素子なので,あえてオーディオ使う理由はないです。 GaNはどうだろう。とにかく速いのが特徴ですからスイッチング用でしょう。 テクニクスが言う通り,デジタルアンプ向きです。

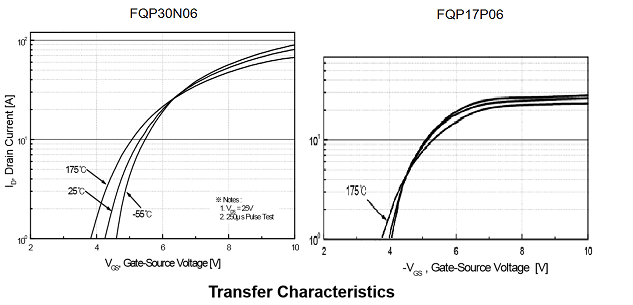

フェアチャイルドの石「FQP17P06」と「FQP30N06」をより詳しく比較してみます。 コンプリメンタリ・ペアとして使えるでしょうか。

基本となるDC特性ですが,グラフの縦軸を合わせるとよく一致しているのがわかります。 10A以上のカーブに差異がみられますが,7A程度までしか使わないので関係ありません。 もっとも使われるであろう1A付近のカーブが一致していることが重要です。 温度特性がやや異なるのが気になるところではあります。

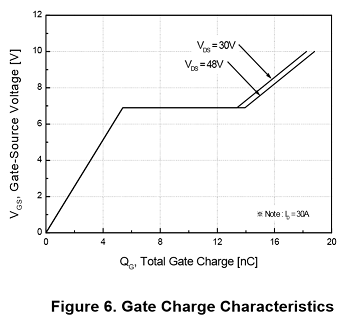

このグラフは動作電流が17Aと30Aでかなり異なるのでその分を差し引いて考える必要があります。 それにしてもゲート駆動容量と閾値電圧はよく一致しています。 結果的に波形の立ち上がりと立下りの動作が近くなり波形の上下対称性がよくなるでしょう。 2次歪みが出にくくなり,立ち上がりの速い信号に対してDC変動が出にくいといった効果が期待できます。

Table:1

|

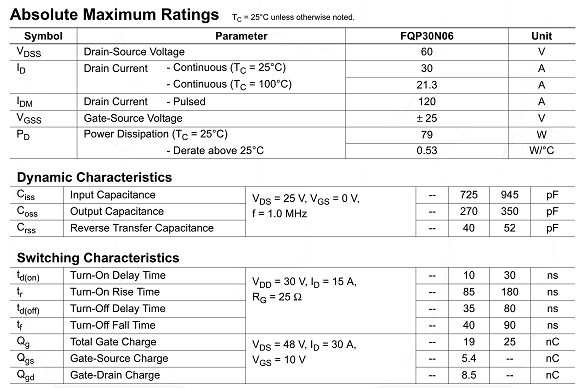

Table:1にFQP30N06の規格を抜粋しました。

ドレイン電流30Aはかなりオーバースペックです。

それでもゲート容量はそれほど大きくありません。

TO-220ですが,79Wの損失を許容しています。

チップ・ケース間の熱抵抗が小さいために高損失に耐えるようです。

とはいえ,ヒートシンクへの取り付けには気を使った方がよいです。

Table:2

|

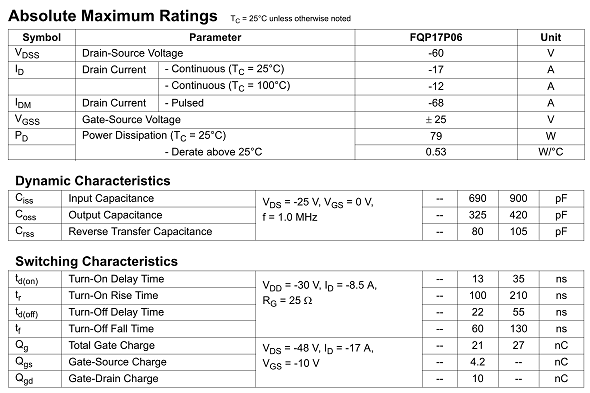

Table:2にFQP17PN06の規格を抜粋しました。

ドレイン電流は17Aなのでちょうどよいです。

Pchとしては高性能だと思います。

PC=79WはFQP30N06と同じです。

入力容量や熱抵抗から考えてチップサイズは同程度と考えられますし,耐圧も60Vと一致しています。

動作速度はPchなので遅いです。仕様書の動作条件が違うので比較は難しいですが,Nch半分というわけではありません。

入力容量やゲートチャージがNchと同等というのがポイントと考えています。

SEPPで高速動作を実現するためにはPch/Nchの速度が一致していることがとても重要です

以上のことから「FQP17P06」と「FQP30N06」はコンプリメンタリ・ペアとして十分通用すると判断しました。 実際に回路を組んでみた印象ですが,矩形波の立ち上がりと立下りが奇跡的に一致していますし,アイドリング時のゲート電圧もどちらもほぼ3.5Vで見事に一致しました。

2-4-2:トランジスタの選定

初段,ドライバ段のバイポーラ・トランジスタは特に指定はありません。 容量が小さくftの高いトランジスタを使うとよいと思います。

試作では定番の2SC1815/2SA1015を使いましたがよく動きました。

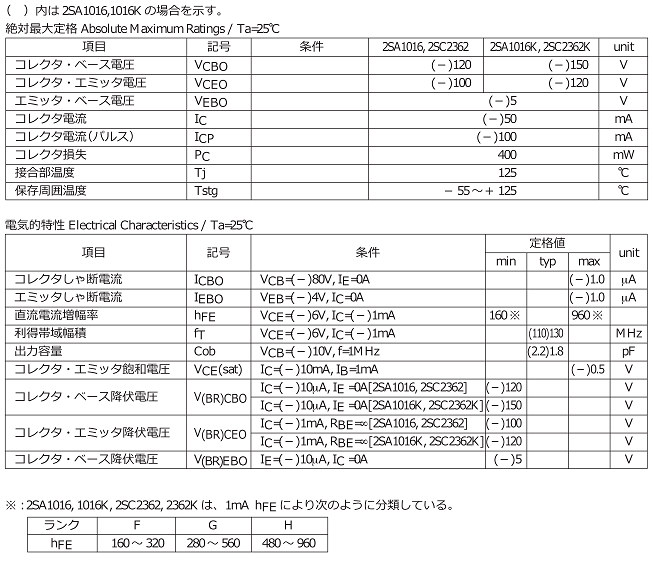

Table:3

|

Table:3に2SC2362/2SA1016の規格を抜粋しました。

ベース電流補償用トランジスタに採用しました。

高耐圧の小信号用トランジスタで,低雑音増幅用とされています。

低雑音を謳ったトランジスタは減少傾向にあるので貴重です。

三洋の石はHfeのリニアリティが良いのが特徴と思っています。

10mAまではほぼ真っ直ぐなので,1/10を目安として1mA前後で使うのが良いとおもいます。

2SC1815でもいいでしょう。

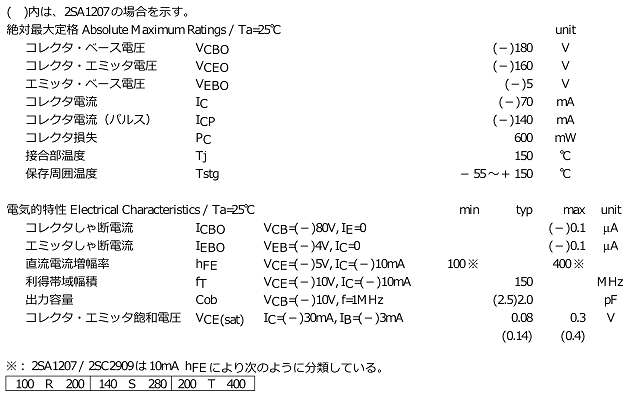

Table:4

|

Table:4に2SC2909/2SA1207の規格を抜粋しました。

初段のVbe補償用,定電流源の折り返し部分に採用しました。

高耐圧のプリドライバ用とされています。

2SC2362より電流を流すことでき,飽和に強いのが特徴(と思っています)。

Hfeリニアリティは20mA程度までとなっています。

入手容易な代替えは2SC1815でしょう。

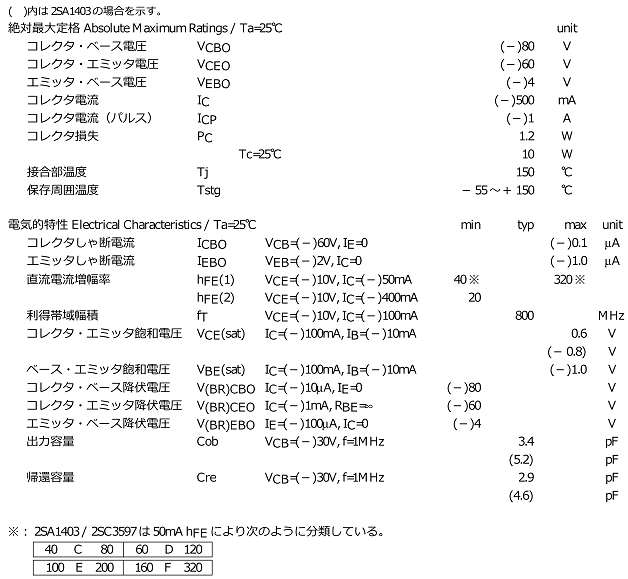

Table:5

|

Table:5に2SC3597/2SA1403の規格を抜粋しました。

初段,カレントミラーに採用しました。

なんでも超高精細CRTディスプレイのビデオ出力用とのことです。

ftが800MHzと高いのが特徴です。

Cobが小さめで電流が流せるということでしょう。

Hfeリニアリティは300mAまでいけます。

PCも1.2Wあるので10mA以上で動作させたい時には好都合です。

2SC2909では定格に不安があるときに活躍すると思われます。

入手容易な代替えは2SC3421か2SC3423でしょうか。

熱くなりますが2SC1815でも大丈夫でした。

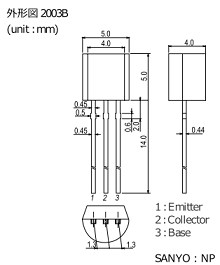

各トランジスタのパッケージを以下に示します。

|

|

|

|

2SC2362/2SA1016 2SC2909/2SA1207 |

2SC3597/2SA1403 | FQP30N06/FQP17PN06 |

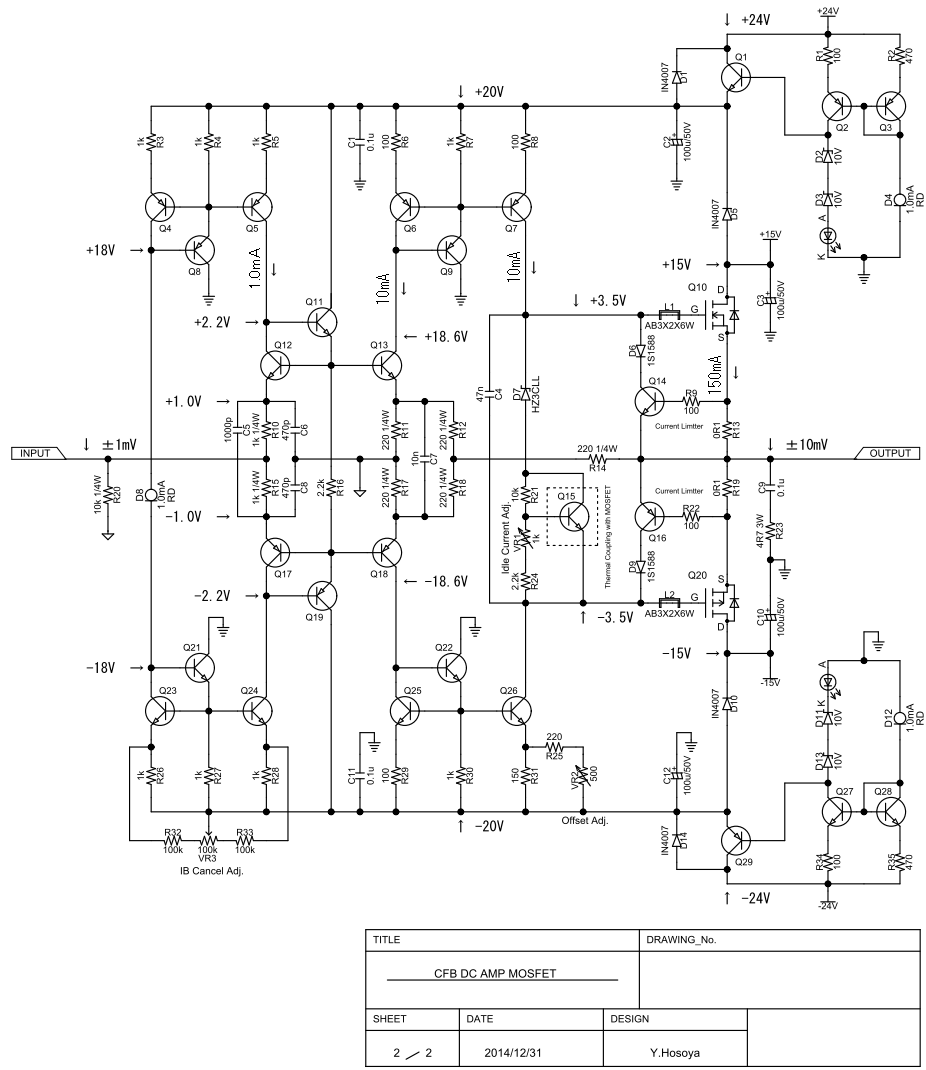

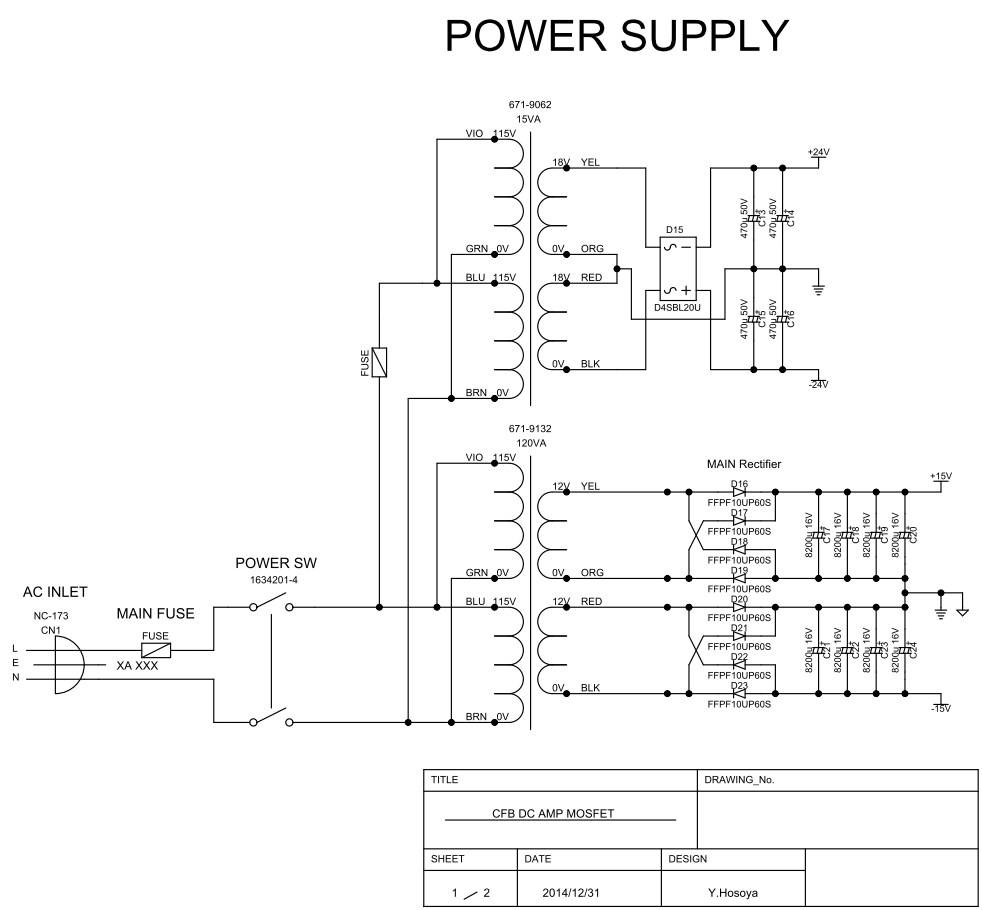

2-5:電源回路

Fig:8 MOSFET出力電流帰還DCアンプ電源回路

Fig:8に電源の回路図を示します。

電源は電圧増幅段用と電力増幅段用の2系統備えています。

必要な出力電圧は12.6V0-Pですが,若干の余裕を見込んで電力増幅段の電源は±15Vとしています。

電力増幅段の電源トランスにはAC115V:12Vの電源トランス使用しています。 AC100Vで使用するので100:10.4となり,√2倍のピーク電圧は14.7Vとなります。 無負荷だとこれより高くなり,定格負荷だとこれより低くなると予想されます。 設計上重要なのは無負荷の場合に電解コンデンサーの耐圧である16Vを超えないこと,また逆に最大出力時に13Vを切らないことです。

2-5-1:ダブル・ブリッジ整流回路を採用

整流方式は正電圧と負電圧にそれぞれ整流ブリッジをひとつづつ使うダブル・ブリッジ整流方式としています。 大電流の信号電流が閉じたループを巡りますので電流の閉じ込め効果が期待できます。

シングル・ブリッジ整流方式は広く使われていますが,DCや低周波を出力した場合にセンタータップにDC電流が流れ,トランスのコアが飽和しやすいという欠点があります。 また,センタータップに大電流の信号電流が流れるので,アンプ全体のGNDが揺すられることになります。

ダブルブリッジ整流方式ではトランスにDCが流れることはないのでコア飽和が起きにくくなります。 トロイダルコア・トランスはEIコア・トランスよりも飽和しやすいのでより効果的だと考えています。

トランスのコアが飽和するとなぜいけないかというと,うなりが発生がするからです。 特に高効率なトロイダルコアやRコア・トランスでは「ブーン」といったうなりが発生しやすくなります。 うなりの発生原因は直流電流による励磁のアンバランスによってBH曲線のバランスが崩れ,AC電流の片側でコアが飽和して過大な励磁電流が発生するためです。 うなりによる弊害はアコースティックノイズの発生はもちろんですが,パルス状の電流によるノイズ輻射も考えられます。

2-5-2:大容量コンデンサで瞬間的な大出力に耐える

フィルターコンデンサは安価に入手した電源用の低インピーダンス品を使っています。 8,200uF/16Vを4パラして片電源あたり32,800uF,合計で65,600uFとしています。16Vと低耐圧なので見た目は小さいですが静電容量は巨大です。

66,000uFという静電容量は100Wクラスのハイエンドクラスのパワーアンプが搭載する容量に相当します。 瞬間的な大電流に限れば300Wクラスのパワーアンプと同等の電流を出力することができます。

2-5-3:接合容量の小さなファースト・リカバリ・ダイオードを採用

整流ダイオードは高耐圧の高速ダイオード(FRD:ファースト・リカバリ・ダイオード)を採用しました。

世間的にはオーディオアンプにSBDを使うことが流行っていますが,接合容量が大きいという宿命ともいえる致命的な欠点があります。 ダイオードもMOSFETと同様にプロセスの微細化をもって性能向上を図っています。 ダイは小型でも接合面積を大きくすれば多くのダイオードを並列にしていることと同等ですので,大電流,低VFを実現できます。 しかし,その分だけ接合容量は増えていきます。

SBDはFRDに比べて10倍以上の接合容量を持ち,パワーアンプに適した大電流品は接合容量が1000pFを超える品種もあります。 SBDはリカバリ・ノイズが出ないと言われていますが,接合容量を充放電する電流は流れます。 また,ダイオードの接合容量が大きいとAC1次側との結合が強くなりAC電源の品質が及ぼす影響が大きくなると考えています。

使用したFRD「FFPF10UP60S」はファースト・リカバリ・ダイオードを超えるウルトラ・ファースト・リカバリ・ダイオードと称しています。 高耐圧600V,高電流容量10Aの定格を持ち,リカバリータイムの代表値は40nsecと高速です。 接合容量は印加電圧によって変化しますが,0Vで51pFと極小です。 対してSBDの例を挙げると,秋月で販売中のSBDブリッジ60V10A「D15XBS6」ですと1Vで1000pFですので200倍の接合容量を持ちます。

条件によって変わる数値をカタログスペックで比較するのは無謀ですが参考にはなります。

2-5-4:電圧増幅段の電源トランス

電圧増幅段の電源トランスにはAC115V:18Vの電源トランス使用しています。 AC100Vで使用しますので100:15.7となり,√2倍のピーク電圧は22.1Vとなります。 負荷が軽いので電圧が上がり,24V程度になります。電源用のコンデンサーの耐圧は余裕を見て50Vとします。

電圧増幅段はハムノイズを最小限にするために安定化が必須となります。 また,MOS FETのゲートを確実にドライブするために電力増幅段の電源電圧より少なくとも5Vは高くする必要があります。 電圧は±24Vを目標としましたが,部品選定の都合で安定化後の電圧が±20Vとなりました。

安定化には定電流源とツエナー・ダイオードによるリップル・フィルターを採用しました。 ツエナー・ダイオードにはノイズ吸収用のコンデンサーをパラ付けするのが一般的ですが,電源投入時の立ち上がり速度を重視するため省きました。 理由は電源投入時の過渡現象として出力段のMOS FETをONさせないために,電力増幅段の電源よりも電圧増幅段の電源を早く立ち上げる必要があるからです。

リップル・フィルターの想定されるリップル除去率は定電流源のインピーダンスとツエナーダイオードの動作抵抗で決まります。 ざっくり100kΩ対100Ωとするとその差は60dBになります。 整流後の電源リップルが1Vならば安定化電源の出力リップルは1mVになります。 アンプのPSRRが60dBほどあるはずなので出力されるノイズは1uV程度になり無視できことになります。

電源トランスの結線も一工夫しています。 1次側と2次側のタップ間の容量を測定し,容量結合が最も少なくなる結線を選んでいます。効果は未確認ですが・・・ シャーシ電位ができるだけ少なくなるように,つまりコンセントからのノイズができるだけはいらないように工夫をしました。

電源トランスが大型になれば1次・2次間の容量結合も大きくなります。 容量結合が大きければシャーシのインピーダンスが低くなりシャーシ電位の影響が大きくなります。 また,接続機器がコンセントから電源を取っている限り,容量結合による巨大なGNDループができてしまいます。 トランスはできるだけ小さくて浮遊容量が少ないものを選びたいです。

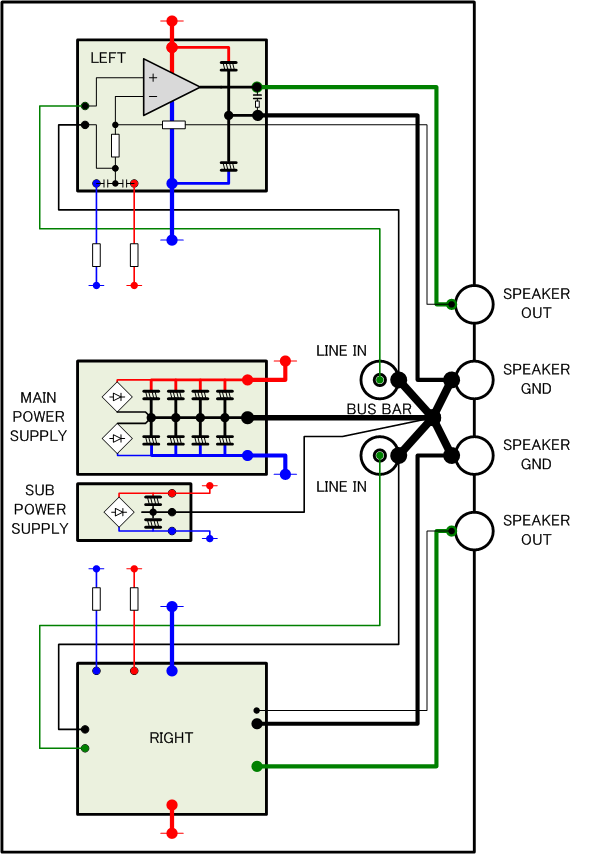

2-6:配線と実装(ステレオアンプのグランド配線)

ステレオアンプではL/RのGNDの引き回しがとても重要になります。 配線の太さや引き回し接続方法によって特性が変化します。 特にクロストーク特性,残留ノイズ,ダンピングファクタに効いてきます。

一方,真空管アンプのGND配線はトランジスタアンプに比べると容易です。 なぜならば,トランスがGNDのアイソレーションを取ってくれるからです。 特に出力端子からNFBをかけない無帰還アンプの場合はトランスの2次側は完全にアイソレーションされますので,GNDの共通電位の影響がなくなります。 真空管アンプが組み立てやすく音が良いと言われる一因になっていると考えています。

2-6-1:ステレオ(L/R)の分離とグランド配線

まず,ステレオアンプの左右チャンネルを完全に分離することはとても困難です。

モノラルアンプを2台使えば完璧!と考えている方も多いでしょう。 しかし,電源コンセントを通じて2台のアンプがつながっています。 DC的には分離できますが,交流的にはループ状の配線ができているのです。

パワーアンプは非常に大きな電源トランスを搭載しますので,トランスの浮遊容量が大きくなってしまいます。 したがってどちらかというとパワーアンプ側を分離するよりも,送り出し機器の左右GNDを分離したほうが効果が高いでしょう。 なぜならば電源トランスが小型なので浮遊容量が小さく漏洩電流が減るからです。

まあそもそもレコードでは左右分離が難しいうえにクロストークもたっぷりありますので,L/Rを分離する意義は少ないです。 ハイレゾは120dB以上のダイナミックレンジを云々しますので影響がありそうです。 とはいえ,チャンネル間クロストークを80dB以上確保するのはなかなか難しいのが現実です。

話が横道にそれましたのでステレオアンプの配線の話に戻します。

2-6-2:グランド配線にまつわるトラブル(ノイズの発生)

GND配線に起因するトラブルとしてまずハム・ノイズの混入が挙げられます。

「ムー」というハム・ノイズだけならばまだしも整流用のダイオードが発するスパイクノイズが飛び込むと「ジー」っという音が混入します。

パワーアンプは自分自身の電源がノイズを発しています。しかもパワーがあるだけにノイズも大きいです。

電源ノイズはGNDに存在する共通インピーダンスから漏れこんできます。 トランスに戻るGND配線はリップル電流が流れていますので他のGND配線から独立させます。 電源部のGND配線はリップルの少ない部分で1点接地します。

リップル電流が流れるGND配線と信号電流が流れるGND配線は共通インピーダンスが最小限となるように明確に区別します。 特にスピーカーから戻ってくるGND配線と整流リップルが流れる整流回路のGND配線には要注意です。

電源トランスはコモンモード・ノイズも発します。 トランスの結線方法を吟味することでコモンモードノイズが最小になるように工夫します。

そして,機器内部でGNDループあるとハムを拾うことになりますので魚の背骨状のGND配線とします。

L/Rの入力端子を離れた位置に配置するのはよくありません。 プリアンプとの接続ケーブルが巨大なGNDループを作ってしまいます。 このGNDループを切断することはできませんので,ループが最小になるように入力のL/R端子はできるだけ近くに配置してGND同士を最短で結線します。

2-6-3:グランド配線にまつわるトラブル(クロストーク悪化)

クロストークを防ぐためにはL/Rで共用しているGND配線は極力短くします。 特に出力段は大電流が流れますので太く・短くが基本になります。 例えば共通インピーダンスが1mΩありそこに1A流れれば1mV発生しますから,もし出力電圧が10Vなら1mVは-80dBになり,これがクロストーク特性を制限します。

2-6-4:グランド配線にまつわるトラブル(特性劣化)

GND配線にまつわる特性劣化で顕著なのがダンピングファクタの劣化です。 出力側を太くしてもGND側が貧弱ならばその抵抗値の分だけダンピングファクタは低下します。 もし帰還回路と出力回路に共通インピーダンスがあったなら電流帰還がかかってしまいダンピングファクターが大きく下がります。

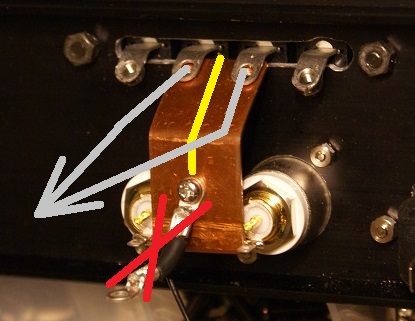

2-6-5:グランド・バスバー

このような様々な条件を同時に満たすためには,まずL/RのGND配線を最短で結ぶこと。次に入力と出力のGND配線も1点に落とします。 結果的にL/Rそれぞれの入力・出力の4本の配線を1点落とすことが得策と思います。 今回はそのためにバスバーを作りました。

真空管アンプには前述した理由によりこのようなバスバーは不必要ですが,トランジスタアンプではGNDの抵抗値を最小限にするためキーパーツになってきます。

ただしこれは最適解ではありませんでした。クロストークが悪化してしまうので,もう少し改善の余地があります。

電源を含めた模式図はこのようになります。

しかし実際のところ,クロストークは残りました。 共通インピーダンスとなるDCRを完全にゼロにできていないのです。

そこで配線をすこし変更してみるとクロストークが低下しました。

共通インピーダンスがどこに残っているのか,それは2本のスピーカーGNDからピッグ・テールのポイントです。

まずピッグ・テールは接続しません。そしてスピーカーのGNDから電源へ2本のGNDを直接配線しました。 これだけでクロストークが低下します。厚さ1mmの銅製とはいえバスバーのDCRが効いているのです。

やはりここら辺の配線が鍵を握っているようです。 さらに改善するためには黄色い線で示すスリットを入れればよさそうです。 実際にやってみましたが効果を測定できていません。

今回初めてステレオ・アンプを作ってみて,トランジスタ・アンプは電源・GNDの配線が非常に重要だということがわかりました。

結果的に実力としては電源由来のリップルノイズはほぼ皆無ですし,左右チャンネルのクロストークは80dB〜90dBは取れているようですのでまずは満足です。

最終手段としてはバランス入力,BTL出力とすればGNDの結線は考えなくてもよいので,完全差動アンプはひとつの回答であると言えます。 ただし,完全差動とする場合は電力増幅段が2倍の数必要になります。音量調整もバランス回路が必要です。 プリアンプやDACもバランス出力に対応している必要があります。 こまったことに結果的にどうしても回路規模が大きくなってしまい,大げさなことになってしまいます。

21:07 2017/09/18:サブ電源の抵抗は入れていません。入れてみる?意味なさそうだけど。

2-7:保護回路

半導体アンプでは以下のような保護回路を装備することがあります。

・DC電圧監視回路

・過電流保護,SOA保護

・過熱保護回路

・クリップ検出

代表的な保護回路はDC電圧監視回路です。 出力にDCが発生するとスピーカーを壊す恐れがあります。 真空管アンプは出力トランスがありますから,出力にDCがでることはありません。 ところが半導体アンプは回路や部品のどこか1ヶ所でも故障が発生するとDC電圧が発生する可能性があります。 DC電圧が発生するとスピーカーは電圧に応じた電力を消費して過熱して故障してしまいます。

スピーカー配線をショートさせてしまうことはよくあるので,過電流の保護は必ず必要です。 半導体は瞬間的な過電流でも破壊してしまいます。 FETは破壊するとショート・モードで故障することが多く,出力にDCが現れスピーカーに大電流が流れてしまいます。

SOA保護回路は過電流保護回路の進化形です。 Safety Operating Area:安全動作領域はパワーデバイスを使用するうえでは重要な設計項目です。 パワーデバイスに印加できる最大電圧はプロセス的な耐圧によってきまり,流せる最大電流は内部配線や内部抵抗によって決まります。 しかし,一般的なパワーデバイスは最大電圧を印加した状態で最大電流を長時間流すことはできません。 自らの発熱によって過熱して破壊してしまうからです。 単純な計算で電源電圧だけを使って最大電力定格内に収まるように電流制限をかけると本来デバイスが持っている最大電流の1/10〜1/100で制限することになってしまいます。 これではもったいないので,パワーデバイスに印加される電圧と流れる電流の双方を監視してSOA内に収まるように制御するとデバイスの能力を使いきることができます。 これがSOA保護です。抵抗を何本か追加すればよいのですが複雑になるので今回は見送りました。

過熱保護回路はアンプの温度を監視する機能です。 アンプの設置状態によってはSOA保護が働かない条件でもオーバーヒートする可能性があります。 熱くなったら止める。熱くないならガンガン働かせる。という保護機能です。 理想的にはパワーデバイスのジャンクション温度を監視したいところです。

クリップ検出はSR用の大出力パワーアンプに搭載されることがあります。 大入力が加わってアンプがクリップすると音楽信号には含まれない大きな高調波が発生します。 これがスピーカー,特にツイーターを破壊することがあります。もちろん聴衆にとっても耳障りです。

さて主に保護したい対象はスピーカーですので,スピーカーをアンプから切り離す回路が必要になります。

メーカー製のアンプは必ずと言ってよいほどスピーカーを切り離す回路が搭載されています。 メーカー製のアンプがユーザーのスピーカーを壊すようなことがあってはいけません。 アンプが故障することなどそもそも滅多に無いのですが,異常時を想定した異常試験は必ず実施します。 この異常試験の際にスピーカーを壊さないために保護回路が必要になってしまうのです。

これが案外厄介です。昔はリレーが使われていましたが,接触不良しやすいという欠点があります。 リレーは大電流用と小電流用が区別されています。 スピーカーは大電流を流すので大電流用を使いますが,大電流用のリレーは大電流を流さないと正しく導通しません。 ところが,普通にアンプを使っていると普段はそれ程大電流が流れないのでやがて導通不良となってしまいます。

そこで最近はMOSFETを使ったスイッチ回路が使われます。接合容量が大きく,高い周波数は通してしまいますが保護回路としては十分機能します。

リレーにせよMOSFETにせよスピーカー配線に何らかのスイッチ素子を入れるわけですから音質上は百害あって一利なしです。 そこで最近は保護回路が働いた時に電源を丸ごと遮断してしまうアンプもあります。 できれば今回も電源遮断回路を入れたかったのですが,場所がありませんでした。次回は入れたいです。

自作アンプでもDC電圧保護と過電流保護は必要です。 しかしこのアンプは電源電圧が低く,最大出力は10W程度です。 ウーハーは50W程度までならば熱くなるにせよ耐えますので,DC電圧監視回路は入れませんでした。 もしかして,交流は振動によって空冷されるからOKで,DCではダメか〜?まあでも10Wなら大丈夫でしょう。

出力をショートするとFETに過大な電流が流れて故障しますので,過電流保護回路は搭載しています。 FETのソースに挿入した0.1Ωで電流を検出して過電流を検知するとトランジスタがONになりFETのゲート電圧を抑制します。 保護回路は帯域制限していないので非常に高速に働きます。保護状態からの復帰もスムースです。

過熱保護は搭載していません。 自作アンプの場合,設置場所を考慮して設計できます。 もしくは熱いアンプが出来上がったら広い場所に置いて風通しを良くすればよいわけです。 ということで必要を感じていません。

クリップは耳で検出できますので必要ありません。 そもそもアンプがクリップするほどの大音量は出しません。 そして音源はDACですし,過剰なゲインを持つプリアンプも使ってませんので,フルスケールでもクリップしません。

今回のアンプの保護回路に関するポリシーをまとめると以下になります。

まずパワーデバイスを壊さないこと。瞬間的に働く電流リミット回路で実現します。

異常な電圧が発生しても電源電圧が低いことからスピーカーが壊れないこと。

異常を感じたらユーザー(自分自身)が電源を切ること。

発煙・発火に至るような異常な電流が連続的に流れた場合はヒューズが切れること。

ヒューズが本当に切れるのか・・・試してません・・・まあ自己責任ですから。

目次へ

Copyright(C) Since 1999 Y.Hosoya. All rights reserved.