/ HOME / DIY / PCM1704 DAC

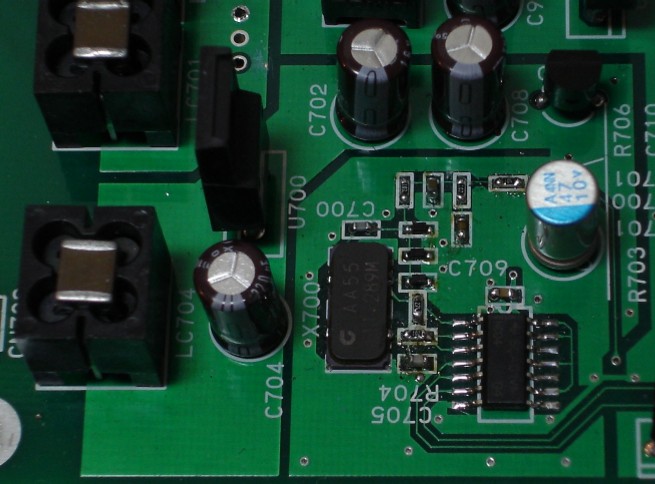

Voltage Control X'Tal Osc

最終更新日2006-02-04

Design Concept

容易に手に入るなかでも確実にジッターが低い発振器は水晶発振器です。 今回は水晶発振器が出力する純度の高いクロックをできるだけ汚さずにDACへ供給することを目的としています。

しかし,SPDIFから入力されるデータは,データを読み取っているCDトランスポートに搭載されているクロック源の周波数を基準にしています。 そのため,同期とってデータを再生するには接続機器に合わせて水晶発振器の発振周波数を変化させなければなりません。 普通の機器は±500ppm(だったかな?)の変動まで許されていますので,最悪でも水晶発振器の発振周波数は±500ppm可変できることが必要になります。

周波数可変の水晶発振器をVCXOと呼びます。 なかなか希望した周波数のVCXOが手に入りにくいので自分で作ることにしました。 水晶は負荷になるキャパシタンスによって共振周波数が微妙に変化しますので,通常は負荷容量が規定されています。 この負荷容量を可変にすることで水晶発振器の発振周波数を微妙にコントロールできます。 印加する電圧を変えると接合部の容量が変化するバラクタダイオードを水晶の負荷として接続して, 外部からバラクタダイオードに加える電圧をコントロールして発振周波数を可変できるようにした発振器がVCXOです。

今回は74HC04を使用してVCXOを作りました。 できるだけノイズの少ない純度の高いクロックが欲しいのですが,ディスクリートで組むのは難しい上に,部品点数が増えますので,CMOSロジックを使用した回路構成にしました。 通常は74HCU04を使うことが多いですが,バラクタダイオードで負荷を変化させて通常は発振しにくい領域まで使いますので,安定に発振する領域を広げるためにバッファが3段で電圧ゲインの高い74HCを使用します。 もちろん異常発振のリスクも高まりますので設計は難しくなります。 ここら辺の定数は現物合わせにするしかなく,基板ができてから部品をとっかえひっかえして試行錯誤するしかありません。 異常発振対策として帰還回路にLPFを設けます。 もちろんここも現物合わせになってしまいます

マスタークロックは分周してfsの倍数が作りやすい11.2896MHz(256fs)にしています。

電源が汚れているとVCXOの発振クロックのジッターが悪化することが懸念されますので,電源は根元である整流部分から他の系統とは独立したVCXO専用電源を設けました。 3端子レギュレターはDC電圧の安定性は優れるものの,出力のノイズが多いことはあまり知られていません。 しかも電源変動を抑えることができる帯域が数10kHzまでしかありませんので,高周波のノイズは素通しになってしまいます。 そこで,トランジスタを使用したリップル除去回路を挿入して,電源から混入するノイズを広帯域にわたって低減しています。

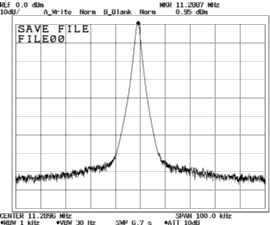

44.1kHz 256fs(11.2896MHz) VCXO Output Spectrum

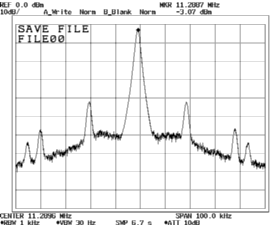

44.1kHz 256fs(11.2896MHz) DIR1703 Output Spectrum

VCXOの発振スペクトラムと,DIR1703が出力するクロックのスペクトラムの比較です。 DIR1703にはCDプレーヤからSPDIFデータを入れています。 VCXOのジッターとSPDIFのジッターを切り分けることはできませんが,かなり派手なスプリアスが出ています。

比較して,VCXOの発振スペクトルはきれいです。 通常の水晶発振器よりは位相ノイズが大きいかもしれませんが,VCXOの可変範囲とはトレードオフの関係にあるといえます。

/ HOME / DIY / PCM1704 DAC