/ HOME / DIY / PCM1704 DAC

嵟廔峏怴擔2006-02-04

崱夞偺DAC偺娞偱偁傞FIFO僶僢僼傽偼TI偺74ACT7804丅 18Bit512抜偺旕摨婜FIFO僶僢僼傽傪嵦梡偟傑偟偨丅

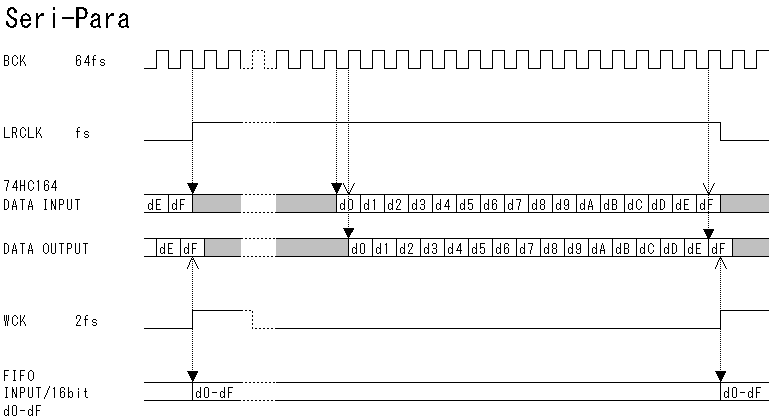

DAIF IC乮崱夞偼DIR1703乯偐傜弌椡偝傟傞 BCK,LRCK,DATA 偼16Bit偺僔儕傾儖僨乕僞側偺偱丆偙偺僨乕僞傪74HC164傪巊梡偟偰僔儕僷儔曄姺傪峴偄丆16bit偺僷儔儗儖僨乕僞偲偟偰FIFO僶僢僼傽偵擖椡偟傑偡丅 FIFO偺儗僕僗僞傊偺彂偒崬傒偼丆FIFO偵擖椡偡傞僋儘僢僋偺棫偪忋偑傝偱峴傢傟傑偡丅 LRCK偼偪傚偆偳僒儞僾儕儞僌偲摍偟偄廃攇悢乮fs乯偱偡偺偱丆嵍塃偺僠儍儞僱儖偺僨乕僞傪撉傒崬傑偣傞偨傔偵偼LRCK偺2攞偵摉偨傞2fs偺僞僀儈儞僌僋儘僢僋偑昁梫偵側傝傑偡丅 偙偺僋儘僢僋傪壖偵儚乕僪僋儘僢僋乮WCK)偲屇傫偱偄傑偡偑丆LRCK偲DATA偑BCK偺棫壓傝偵摨婜偟偰偄傞偺偱WCK傕棫壓傝偵摨婜偟偰偄傞昁梫偑偁傝傑偡丅 崱夞偼僔僼僩儗僕僗僞偵LRCK傪擖椡偟BCK偱扏偄偰抶墑偟偨LRCK傪嶌傝丆尦偺LRCK偲EXOR傪庢傞偙偲偱2fs偺僞僀儈儞僌傪嶌傝傑偟偨丅 扨弮偵BCK傪斀揮偟偰暘廃偟偰偄偭偰傕椙偄偺偱偡偑丆LRCK偲偳偺傛偆偵摨婜傪庢傟偽偄偄偺偐巚偄晜偐偽側偐偭偨偺偱慜弎偺曽朄傪偲偭偰偄傑偡丅

CS8414傪巊偊偽丆LRCK偺戙傢傝偵WCK傪弌偡儌乕僪偑偁傝傑偡偺偱偙偺夞楬偼昁梫偁傝傑偣傫丅

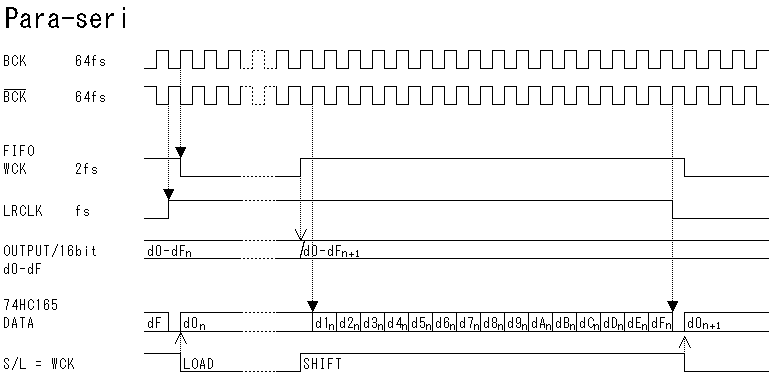

FIFO偺撪晹儗僕僗僞偵撉傒崬傑傟偨僨乕僞偺撉傒弌偟偼VCXO偺僋儘僢僋傪暘廃偟偰嶌偭偨2fs偺僋儘僢僋乮WCK)偱峴偭偰偄傑偡丅 2fs偺僋儘僢僋傪FIFO偵擖椡偡傞偲棫偪忋偑傝偵摨婜偟偰撪晹偺儗僕僗僞偵曐懚偝傟偰偄偨僨乕僞偑撉傒弌偣傑偡丅 撉傒弌偟偨僨乕僞傪74HC165偵擖椡偟偰僷儔僔儕曄姺傪峴偄傑偡丅 僷儔僔儕曄姺偺婎弨偵側傞僋儘僢僋偼VCXO傪暘廃偟偰嶌偭偨BCK偵側傝傑偡丅 僷儔僔儕曄姺奐巒偺僞僀儈儞僌偼WCK偱偲偭偰偄傑偡丅 僷儔僔儕曄姺偝傟偨DATA傪DF1704偵擖椡偡傞傢偗偱偡偑丆DF1704偵擖椡偡傞DATA偼BCK偺棫壓傝婎弨偱側偗傟偽側傝傑偣傫偺偱拲堄偑昁梫偱偡丅

偙偺DAC偺儈僜偼丆側傫偲偄偭偰傕撉傒弌偟懁偵VCXO傪巊梡偟偰偄傞偙偲偱偡丅 VCXO偼Q偺崅偄悈徎儀乕僗偺敪怳婍偱偡偺偱僋儘僢僋偺弮搙偼嵟崅偵傛偄偱偡丅 DAIF IC偺撪晹VCO側偳偲偼斾妑偵側傝傑偣傫偟丆儖價僕僂儉傗傜GPS塹惎傗傜傪儕僼傽儗儞僗偵偟偨僋儘僢僋惗惉婡婍傕幚嵺偵弌椡偝傟傞僋儘僢僋偼悈徎傪巊梡偟偨VCXO側偺偱偦傟傎偳堘偄偑偁傞偲偼峫偊傜傟傑偣傫丅

256fs偺11.2896MHz傪74HC161偱暘廃偡傞偲BCK,WCK,LRCK偼BCK偺棫壓傝偵摨婜偟偰弌椡偝傟傞傛偆偵尒偊傑偡 LRCK偼BCK偺棫壓傝婎弨偱傛偄偺偱偡偑丆僨乕僞偺撉傒弌偟偲WCK偼LRCK偐傜BCK偺敿僋儘僢僋抶傟偨僞僀儈儞僌偑昁梫偵側傞偙偲偑僞僀儈儞僌僠儍乕僩偐傜傢偐傝傑偡丅 74HC74偵傛偭偰WCK傪BCK偺棫偪忋偑傝偱扏偒側偍偟丆FIFO偵偼BCK偺斀揮僋儘僢僋傪嫙媼偟傑偡丅

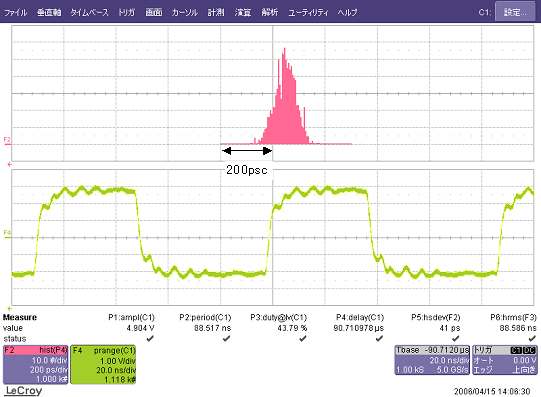

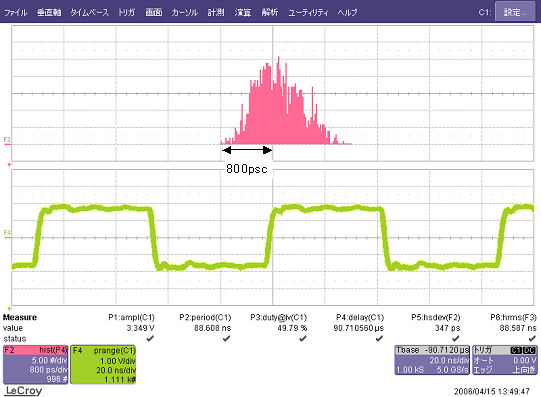

幚嵺偵偳偺偔傜偄Jitter偵嵎偑偁傞偺偐應掕偟偰傒傑偟偨丅

VCXO(冃 = 41psec) 44.1kHz 256fs(11.2896MHz) Long Term Jitter (1024CLK)

DIR1703(冃 = 347psec) 44.1kHz 256fs(11.2896MHz) Long Term Jitter (1024CLK)

忋婰偺2枃偺恾偼僩儕僈乕傪偐偗偨僄僢僕偐傜1024僋儘僢僋屻偺僄僢僕偑偳傟偩偗梙傟偰偄傞偐傪昡壙偟偨寢壥偱偡丅 僋儘僢僋廃攇悢偑憗偄偲1僋儘僢僋偺僕僢僞乕傪寁應偟傛偆偲偟偰傕丆暘夝擻偑峳偔側偭偰偟傑偄惓妋偵寁應偡傞偙偲偑偱偒傑偣傫丅 偦偙偱儘儞僌僞乕儉僕僢僞乕偲偄偆寁應庤朄傪梡偄偰昡壙傪峴偭偰傒傑偟偨丅 PLL偺摥偒偵傛偭偰偁傞僋儘僢僋悢埲忋偼僕僢僞乕偑堦掕偵側傝傑偡偑丆崱夞偼娙堈揑偵1024僋儘僢僋偱偺僕僢僞乕傪斾妑偟偰傒傑偟偨丅

偙偺寢壥偐傜偼SPDIF偑梙傟偰偄傞偺偐丆VCO偺僕僢僞乕偑尒偊偰偄傞偺偐偼敾抐偑偮偒傑偣傫偑丆 揱憲宯偺梙傟偼SpAct偑傎偲傫偳媧廂偟偰偄傑偡偺偱丆DIR1703撪憼偺VCO偺僕僢僞乕偑尒偊偰偄傞偲峫偊偰偄偄偲巚偄傑偡丅

VCXO偺曽偑僕僢僞乕41psec偲側偭偰偄傑偡偑丆壗僋儘僢僋暘傪寁應偟偰傕41psec晅嬤偺抣偑弌傞偺偱丆寁應宯偺尷奅偲峫偊傜傟傑偡丅

偙偺悢帤偼1024僋儘僢僋暘傪壛嶼偟偨昗弨曃嵎傪帵偟偰偄偰侾冃偺抣乮幚岠抣乯偱偡丅Peak-Peak偺僕僢僞乕偼6.6攞偟偰1/1024偟偨抣偵側傝傑偡丅

尰忬VCXO偵擖椡偡傞惂屼怣崋偼1Hz埲壓偵僼傿儖僞儕儞僌偟偰偄傑偡丅 512抜偺僶僢僼傽偑偁傝傑偡偺偱丆擖椡懁偺僋儘僢僋偑梙傟偰傕娙扨偵摨婜偑奜傟傞偙偲偼偁傝傑偣傫丅 椺偊偽丆僋儘僢僋偑100ppm偢傟偨偲偡傞偲丆嵍塃僠儍儞僱儖偁傞偺偱FIFO偺僋儘僢僋偼88.2kHz偵側傝傑偡丅 100ppm偱偼8.82Hz丆1昩娫偵8.82僋儘僢僋偢傟傞偲偄偆偙偲偵側傝傑偡丅 FIFO偑512抜偁傝傑偡偺偱丆512 / 8.82 = 58[sec]帩偪偙偨偊傞偙偲偑弌棃傑偡丅 偦傕偦傕VCXO偺壜曄斖埻偑亇100ppm偲峫偊傞偲悽偺拞偺悈徎敪怳婍偺惛搙傕摨掱搙偲峫偊傜傟傑偡偺偱丆VCXO偺敪怳廃攇悢偲SPDIF偐傜暅挷偟偨僋儘僢僋偑100ppm埲忋僘儗傞偙偲偼側偐側偐柍偄偲巚偄傑偡丅

/ HOME / DIY / PCM1704 DAC