/ HOME / DIY / PCM1704 DAC

最終更新日2015-01-12

非同期FIFOバッファ部 2006-04-16 update

PCM1704 DAC 部 2006-02-04 update

BB(TI)のPCM1704というチップを使ってDACを組んでみました。

PCM1704は著名なCDプレーヤなどにも使われている定評のあるDACです。

DF1704というデジタルフィルターと組み合わせて最大8倍オーバーサンプリングのDACになります。

只のDACじゃつまらないので,ジッター低減に努めてみることにしました。

どんなに高性能なDAIFを使用してもSPDIFを受信して動く限り,マスタークロックのジッターを減らすには限界があります。

ジッターはアナログ信号に乗ってくるノイズと同じように一度信号に加わってしまうと取り除くのは容易ではありません。

信号を伝達する伝送系やICをひとつ通過するだけでもジッターは付加されていきます。

容易に手に入る最も低ジッターな発振器である水晶発振器をDAC ICの近くに配置してバッファや伝送系の影響をできるだけ排除することを目指して設計を行いました。

水晶発振器と入力データの同期が取れないとデータの受け渡しができません。

そこで今回はFIFOバッファとVCXOを使用して入力データは非同期にデータを受け渡す構成にしてみました。

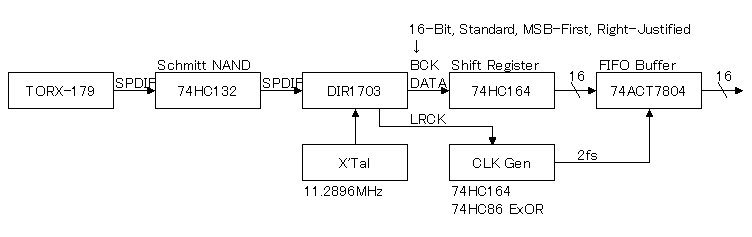

前半部分のブロック図(FIFOに入力するまで)

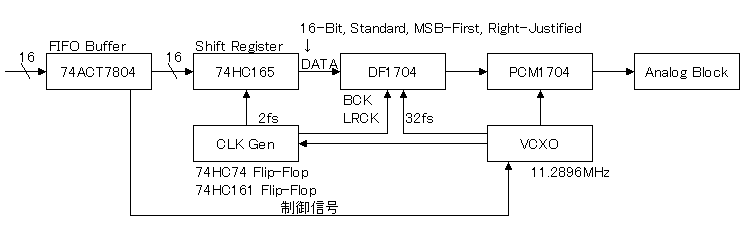

後半部分のブロック図(FIFOから出力されたあと)

SPDIFをDAIFで復調したBCK,LRCK,DATAをシリパラ変換してFIFOに入力します。

FIFOの読み出しはVCXO基準に作った2fsのクロックです。

PCM1704へはVCXOの発振クロックを直接入力しますので,ジッターは最小限になります。

VCXOの周波数を変化させる制御信号はFIFOから取り出します。ここが秘密のミソ。

VCXOの制御信号はFcが1Hz以下のパッシブLPFで厳重にノイズを落としています。

結果,可聴周波数外の低い周波数でとてもゆるやかに追従する緩慢なPLLが掛かっている状態になります。

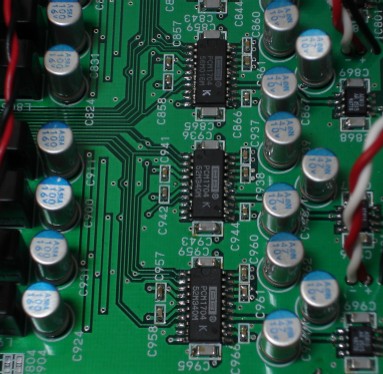

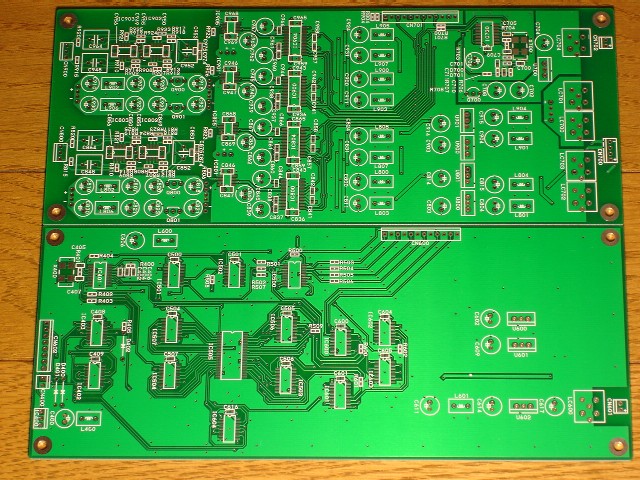

基板も自分で起こしました。

こんなかんじのケースにおさまっています。

いや,ちゃんと動いてますよ。実際に。VCXOもロックしてるし。

SpActがいまいちなんで気に入らないけど。まあ,VCXOがちゃんと追従するからいいか。

VCXOの可変範囲は数百ppmですが,たいていのトランスポートでもロックするはずです。

固定クロックによるメモリバッファと違い,トランポートのクロック周波数に合わせてDACのクロック周波数が追従するので,音切れや音飛びの心配はありません。

純粋な水晶発振器とVCXOの違いは負荷容量に使用するコンデンサーの容量を外部から印加する電圧で可変できるかどうかです。

今回作ったVCXOはバラクタダイオードを使用して負荷容量を可変しています。

ルビジウム発振器やGPSを使用した発振器も基準になる時間軸は高精度ですが,実際に出力されるクロックは水晶ベースのVCXOを使用しています。

水晶ベースのVCXOの能力を100%発揮するために必要なのは,低ノイズ電源と,低ノイズ制御信号です。

電源はトランジスタによるリップルフィルタ,制御信号はパッシブLPFを使用して数Hz以上のノイズを遮断しています。

/ HOME / DIY / PCM1704 DAC