/ HOME / DIY / PCM1704 DAC

最終更新日2006-03-21

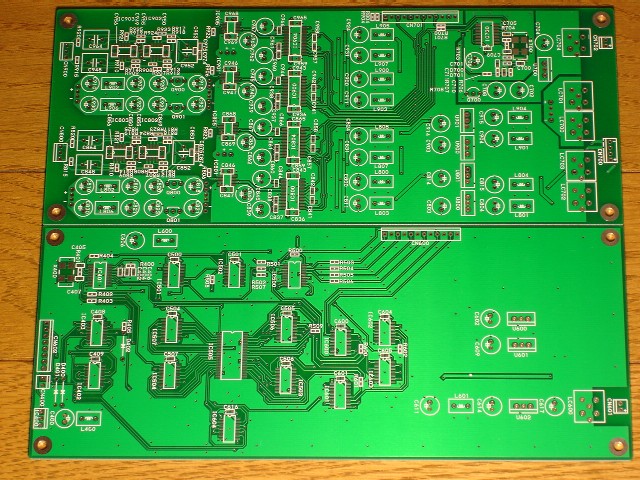

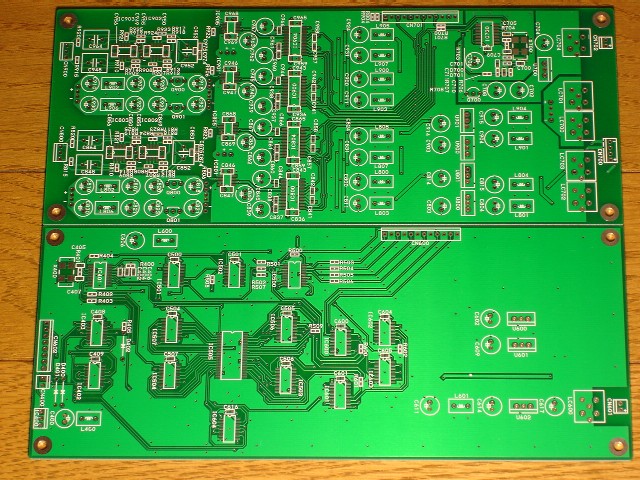

基板が届いただよ。

個人でもこんな基板を起こせる時代になったかと思うとなかなか萌え〜な感じ。

今回は欲張らずに両面基板にしておいた。

本当は4層にしたいのだが,高くなるのでやめておいた。

4層であれば100MHz以上を扱う場合でも容易に性能を出すことができる。

両面だとパターンをかなり吟味しないと基板の動作を保証できなくなる可能性も考えられる

アマチュアイズムを発揮してパターンにこだわりぬくことで両面でも4層と同等の性能が出るようにじっくり取り組んだ。

まあ,時間はあるわけでお金がかからないほうが重要である。

といってもこの基板には相当の時間がかかった。

なにせ,CADを使うのも初めてなので知らない用語に戸惑いながら結局,半年くらいあーでもないこーでもないやっていたのではないだろうか

あとは実装してあちこち波形を見るだけである。

一発完動すると良いのだが。。

デジタルはとにかく輻射ノイズを減らすこと。

アナログはノイズをもらわないこと。

デジタル系はパスコンを直近に配置して,ベタアース面積をできるだけ大きくする。

ICのすぐ下面はベタアース面とする。

ICの足へつながる配線は外側へ引き出す。ICの下面で配線すると改修できなくなってしまうので。

配線は45度配線が基本。一部の遅い信号はこの限りではないが。。

重要な信号線(CLK)等はリターンパスを明確にして,必要ならばガードパターンを設ける

一方アナログ系はノイズを喰らわないことを第一に設計した。

広帯域信号が通る部分はGNDインピーダンス低減のためにベタアースの徹底を行ったが,オーディオ帯域では逆にICの近くに導体を置かないように設計

最低限電源の低インピーダンス化を図りつつ,振動が加わった際に発生する誘導性の結合による信号劣化をなくすように工夫した。

また,音声ループは最小限の面積になるようにパターンを引き,ノイズを受けにくいようにしている。

バランス伝送を考えているので,正相信号と逆相信号でパターンの差異が僅少になるようにパターンを工夫。

ってなとこか・・・

シルクが一部逆になっていたな。。。

あとは無理矢理パターンを引くとベタアースが寸断されてしまうところはあえて手配線を選択したので,アナログ系の電源は自分でジャンパーを飛ばす必要がある。

これもアマチュアならではの発想で,4層基板を使わない工夫のうちのひとつだ。

ところで,この基板いくつかバグがあった。

DIR1703の動作モード設定をまず間違えた。

供給するクロックが11.2896MHzなので,256fsに設定しないといけなかったのだが,間違えた。

SCF1=LOW,SCF0=HIGHにしないいけなかった。

つぎのバグは,LRCKの配線忘れ。

TPを設けていたのだが,これをクロック生成ブロックにつなげていなかった。

そもそもWCKはBCKを分周して作るつもりだったが,後からLRCKとDelayをかけたLRCKのEXORに変更したのに,LRCKの配線を忘れていた。

一番致命的だったのが,FIFOの出口のパラシリ変換部分。

同期カウンタによる分周回路の動作がよく理解できていなかったので,WCKとLRCKがBCKの立下りに同期して出てくるとは夢にも思わなかった。

また,パラシリ変換に使用している74HC165の動作を1CLK分勘違いしていた。

LRCKに対してWCKを1BCK分遅らせる必要があった。

ということで,改修は3箇所。

/ HOME / DIY / PCM1704 DAC